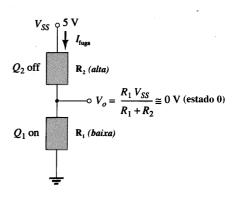

# Transistores de Efeito de Campo

5

$I_{DSS}/V_P$

# 5.1 INTRODUÇÃO

O transistor de efeito de campo, abreviado por FET (direto do inglês, Field-Effect Transistor), é um dispositivo de três terminais, utilizado em várias aplicações e que realiza, em larga escala, muitas das funções do TBJ descritas nos Caps. 3 e 4. Embora haja diferenças importantes entre os dois tipos de dispositivos, verificam-se também muitas semelhanças que serão mostradas nas seções seguintes.

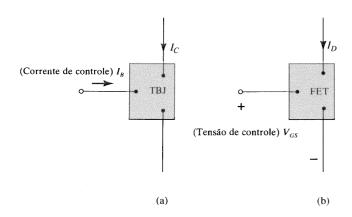

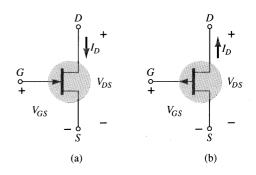

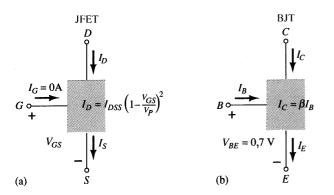

A diferença fundamental entre os dois tipos de transistores é o fato de o TBJ ser um dispositivo controlado a corrente, como mostrado na Fig. 5.1a, enquanto que o JFET é um dispositivo controlado a tensão, conforme a Fig. 5.1b. Em outras palavras, a corrente  $I_c$  na Fig. 5.1a é a função direta do nível de  $I_B$ . Para o FET, a corrente I será função da tensão  $V_{GS}$  aplicada do circuito de entrada, como mostra a Fig. 5.1b. Em cada caso, a corrente do circuito de saída está sendo controlada por um parâmetro do circuito de entrada — em um caso, o nível de corrente, e no outro, a tensão aplicada.

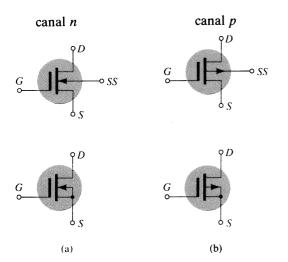

Assim como existem transistores bipolares npn e pnp, existem transistores de efeito de campo de canal n e canal p. Entretanto, é importante observar que o TBJ é um dispositivo bipolar — o prefixo bi- revelando que o nível de condução é função de dois portadores de carga, elétrons e buracos. O FET é um dispositivo unipolar, dependendo somente da condução realizada por elétrons (canal n) ou buracos (canal p).

Fig. 5.1 (a) Amplificadores controlados a corrente e (b) controlados a tensão.

O termo "efeito de campo" escolhido para a denominação do dispositivo merece alguma interpretação. Todos conhecemos a capacidade de um ímã permanente atrair limalhas de ferro sem a necessidade de contato. O campo magnético do ímã permanente envolve as limalhas e as atrai, por meio das linhas de fluxo magnéticas, que realizam o trabalho com o menor esforço possível. Para o FET, um *campo elétrico* é estabelecido pelas cargas presentes, que controlarão o caminho de condução do circuito de saída sem a necessidade de um contato entre as quantidades controladoras e controladas.

Quando se apresenta um dispositivo com conjunto de aplicações semelhantes às de um outro já mostrado, há uma tendência natural de se comparar algumas das características gerais de um dispositivo com as do outro. Uma das características mais importantes do FET é a sua alta impedância de entrada. Com níveis que variam de 1 até várias centenas de megaohms, podese afirmar que sua impedância de entrada é consideravelmente maior do que a de configurações com TBJ — uma característica muito importante a ser considerada em projetos de sistemas de amplificação linear. Por outro lado, o TBJ apresenta sensibilidade muito maior às variações no sinal aplicado. Em outras palavras, a variação na corrente de saída é tipicamente maior para os TBJs do que para os FETs, para uma mesma variação no sinal de entrada. Por isso, os ganhos de tensão dos amplificadores com TBJ são normalmente maiores do que os verificados para os amplificadores com FET. Em geral, os FETs são mais estáveis com relação à temperatura do que os TBJs, e, em geral, são menores fisicamente do que os TBJs — característica particularmente útil na construção de circuitos integrados (CI). As características de construção de alguns FETs, entretanto, podem fazê-los mais sensíveis ao manuseio do que os TBJs.

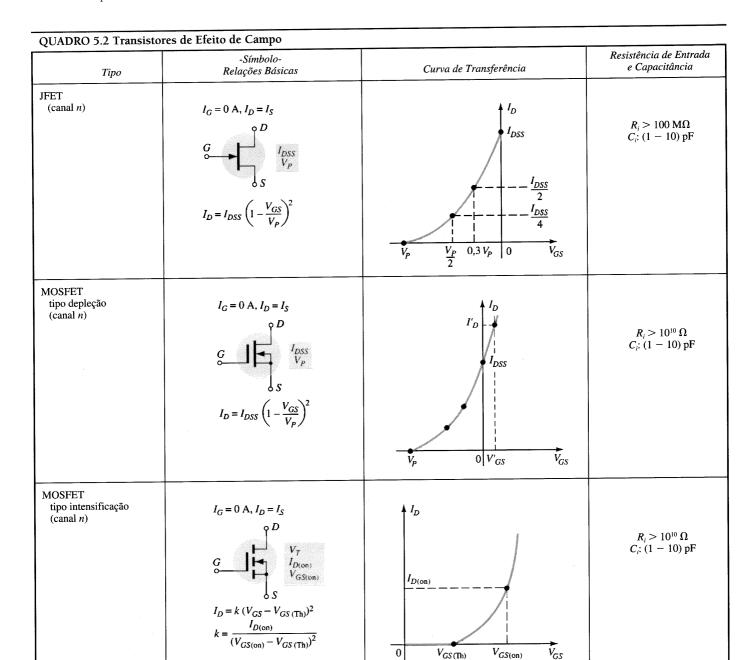

Dois tipos de FETs serão introduzidos neste capítulo: o *transistor de junção por efeito de campo* (JFET) e o *transistor de efeito de campo metal-óxido-semicondutor* (MOSFET). A categoria MOSFET será desmembrada em dois tipos, depleção e intensificação, descritos posteriormente. O transistor MOSFET tornou-se um dos dispositivos mais importantes utilizados no projeto e construção de circuitos integrados para computadores digitais. É termicamente estável, além de outras características que o destacam em projetos de circuitos para computadores. Entretanto, como elemento discreto em um encapsulamento tipo caneca, ele deve ser manuseado com cuidado (observação discutida em seção posterior).

$I_{DSS}/V_{P}$

Em 1955, os Drs. Ian Munro Ross (frente) e G. C. Dacey desenvolveram conjuntamente um procedimento experimental para determinar as características de um transistor de efeito de campo. (Cortesia da AT&T Archives.)

A construção e características do FET serão abordadas neste capítulo, enquanto que as configurações de polarização serão apresentadas no Cap. 6. A análise feita no Cap. 4 utilizando TBJs será útil na dedução de importantes equações, e na compreensão dos resultados obtidos para os circuitos com FET.

# 5.2 CONSTRUÇÃO E CARACTERÍSTICAS DO IFET

Como indicado anteriormente, o JFET é um dispositivo de três terminais, com um terminal capaz de controlar o nível de corrente entre os outros dois. Na nossa discussão sobre o TBJ, o transistor npn foi empregado durante a maior parte da análise e projeto, com uma seção dedicada ao efeito da utilização do transistor pnp. Para o transistor JFET, o dispositivo de canal n será o mais empregado na análise, enquanto que para o dispositivo de canal p só serão dedicados alguns parágrafos e seções.

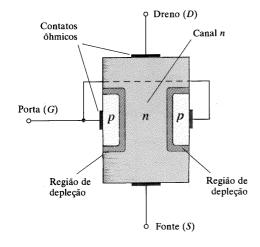

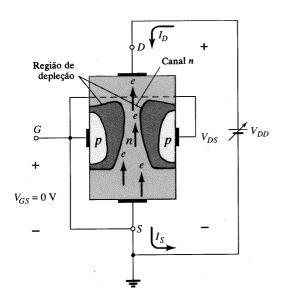

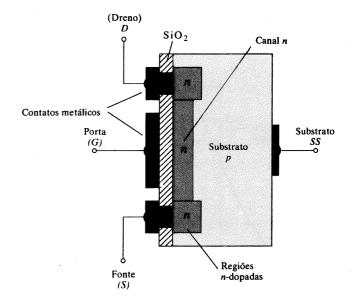

A construção básica do JFET de canal *n* é mostrada na Fig. 5.2. Observe que a maior parte da estrutura é composta do material tipo n, formando o canal entre as camadas imersas de mate-

Fig. 5.2 Transistor de efeito de campo de junção (JFET).

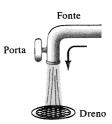

Fig. 5.3 Analogia do fluxo de água para o mecanismo do JFET.

rial tipo p. A parte superior do canal tipo n está conectada através de um contato ôhmico ao terminal denominado dreno (D), enquanto que a extremidade inferior do mesmo material está ligada através de um contato ôhmico ao terminal referido como fonte (S). Os dois materiais tipo p estão ligados entre si e ao terminal porta (G). Em resumo, portanto, o dreno e a fonte estão conectados aos extremos do canal tipo n e a porta às duas camadas do material tipo p. Sem um potencial aplicado, as duas junções *p-n* do JFET estão sob condições de não-polarização. O resultado é uma região de depleção em cada junção, como mostrado na Fig. 5.2, que se assemelha à mesma região de um diodo sob condições de não-polarização. Lembre ainda que uma região de depleção não contém portadores livres, e portanto não permite a condução através da região.

As analogias são raramente perfeitas e às vezes podem confundir, mas a analogia da água da Fig. 5.3 apresenta um sentido para o controle feito pelo terminal de porta e para a terminologia aplicada aos terminais do dispositivo. A fonte de pressão da água pode ser associada à tensão aplicada do dreno para a fonte, e esta estabelecerá um fluxo de água (elétrons) saindo da torneira (fonte). A "porta", por meio de um sinal aplicado (potencial) controla o fluxo de água (carga) para o "dreno". Os terminais de dreno e fonte situam-se em extremidades opostas do canal n da maneira mostrada na Fig. 5.2, isto porque a terminologia é definida para o fluxo de elétrons.

# $V_{GS} = 0 \text{ V}, V_{DS} \text{ Maior que Zero}$

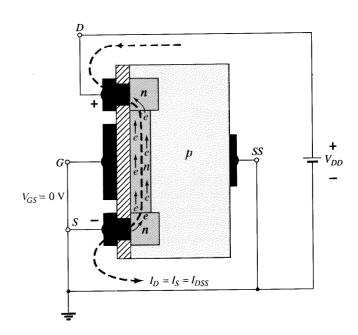

Na Fig. 5.4 uma tensão positiva  $V_{DS}$  foi aplicada através do canal, e a porta foi conectada diretamente à fonte, estabelecendo a condição  $V_{GS} = 0$  V. O resultado é o terminal de porta e fonte no mesmo potencial, e uma região de depleção na extremidade inferior de cada material p, semelhante à distribuição encontrada para a situação de não-polarização da Fig. 5.2. No instante em que a tensão  $V_{DD}$  (=  $V_{DS}$ ) é aplicada, os elétrons fluem para o terminal de dreno, estabelecendo a corrente convencional  $I_D$ , com o sentido definido pela Fig. 5.4. O caminho do fluxo de cargas revela claramente que as correntes de dreno e fonte são equivalentes ( $I_D = I_S$ ). Sob as condições mostradas na Fig. 5.4, o fluxo de cargas não é restringido, e limitado apenas pela resistência do canal n entre o dreno e a fonte.

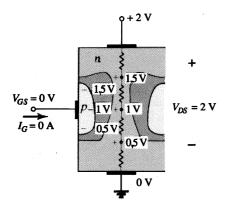

É importante observar que a região de depleção é mais larga na parte superior, em ambos os materiais tipo p. Este fato é mais bem explicado com o auxílio da Fig. 5.5. Assumindo uma resistência uniforme no canal n, ela pode ser distribuída da maneira mostrada na Fig. 5.5. A corrente  $I_D$  estabelecerá níveis de tensão ao longo do canal, como indicado na mesma figura. O resultado é que a região superior do material tipo p estará reversamente polarizada em cerca de 1,5 V, enquanto que a região inferior estará

Fig. 5.4 JFET para  $V_{GS} = 0 \text{ V e } V_{DS} > 0 \text{ V}.$

reversamente polarizada por apenas 0,5 V. Lembre da análise da operação do diodo que, quanto maior a tensão reversa aplicada, mais larga é a região de depleção — justificando a distribuição da região de depleção mostrada na Fig. 5.5. Devido ao fato de a junção *p-n* estar reversamente polarizada, a corrente de porta é zero ampères, como mostrado na mesma figura. Esta característica do JFET é bastante relevante.

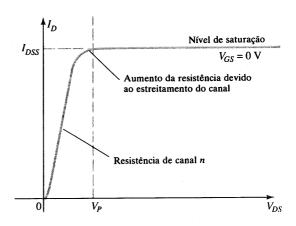

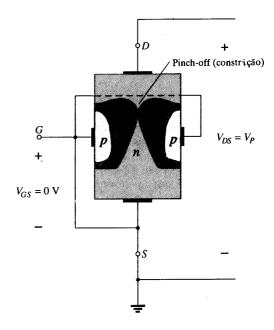

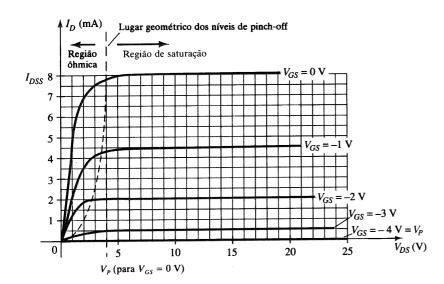

Na medida em que a tensão  $V_{DS}$  aumenta de 0 para alguns volts, a corrente aumenta como previsto pela lei de Ohm, e o gráfico de  $I_D$  versus  $V_{DS}$  tem a forma mostrada na Fig. 5.6. A relativa linearidade da curva revela que, para a região de baixos valores de  $V_{DS}$ , a resistência é absolutamente constante. Quando  $V_{DS}$  aumenta de valor e se aproxima do nível  $V_p$ , na Fig. 5.6, as regiões de depleção da Fig. 5.4 se alargam, provocando considerável redução na largura do canal. Isto acarreta um aumento na resistência do canal, representado na curva da Fig. 5.6. Quanto mais horizontal a curva, maior é a resistência, e no limite tem-se uma resistência "infinita". Se a tensão  $V_{DS}$  for elevada a um nível onde as duas regiões de depleção parecem se "tocar", como mostrado na Fig. 5.7, resulta na condição de *pinch-off*. O nível de  $V_{DS}$  que estabelece esta condição é referido como tensão de constrição (do inglês, *pinch-off*) e é denotado por  $V_p$ , como mostra a Fig. 5.6.

**Fig. 5.5** Variação dos potenciais reversos de polarização através da junção *p-n* de um canal *n* do JFET.

Fig. 5.6  $I_D$  versus  $V_{DS}$  para  $V_{GS} = 0$ V.

Na verdade, o termo "pinch-off" é inapropriado, sugerindo que a corrente é cortada e cai a zero A. Entretanto, como mostrado na Fig. 5.6, este é o caso extremo —  $I_D$  mantém um nível de saturação definido por  $I_{DSS}$  na Fig. 5.6. Na verdade, ainda existe um canal muito estreito, com uma corrente de altíssima densidade. O fato de  $I_D$  não ser cortada no pinch-off e manter o nível de saturação indicado na Fig. 5.6 é verificado pelo seguinte argumento: a ausência de uma corrente de dreno impossibilitaria a existência de diferentes níveis de potencial através do canal n, e não estabeleceria os níveis de tensão reversos ao longo da junção p-n. Com isto, haveria a perda da distribuição da região de depleção que, em primeiro lugar, originou o pinch-off.

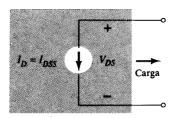

À medida que  $V_{DS}$  cresce e se afasta de  $V_p$ , a região de confronto entre as duas regiões de depleção aumenta em comprimento ao longo do canal, mas o nível de  $I_D$  permanece essencialmente o mesmo. Em resumo, portanto, uma vez estabelecido  $V_{DS} > V_p$ , o JFET apresenta as características de uma fonte de corrente. Como mostrado na Fig. 5.8, a corrente é constante em  $I_D = I_{DSS}$ , mas a tensão  $V_{DS}$  (para níveis  $V_p$ ) é determinada pela carga empregada.

A escolha da notação  $I_{DSS}$  vem do fato de a corrente ser do Dreno para Fonte (Source), com um curto-circuito (Short-circuit)

**Fig. 5.7** Pinch-off  $(V_{GS} = 0 \text{ V}, V_{DS} = V_p)$ .

Fig. 5.8 Fonte de corrente equivalente para  $V_{GS} = 0 \text{ V}, V_{DS} > V_{p}$ .

da porta para a fonte. Se continuarmos a investigar as características do dispositivo, acharemos que:

$I_{DSS}$  é a corrente máxima de dreno para um JFET, e é definido pela condição  $V_{GS}=0$  V e  $V_{DS}>|V_p|$ .

Observe na Fig. 5.6 que  $V_{GS} = 0$  V para toda a curva. Os próximos parágrafos descreverão como a curva característica da Fig. 5.6 é afetada por variações no nível de  $V_{GS}$ .

# $V_{GS} < 0 \text{ V}$

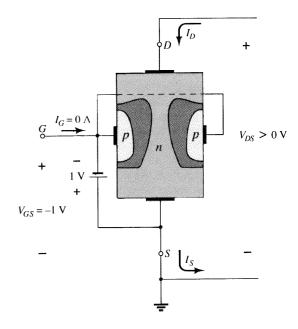

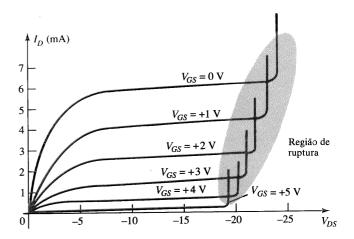

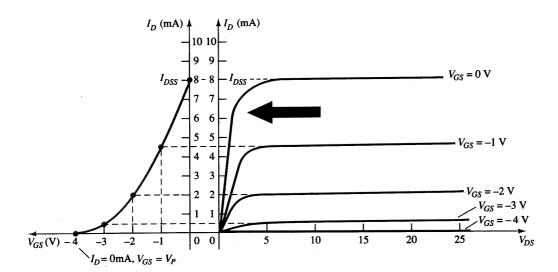

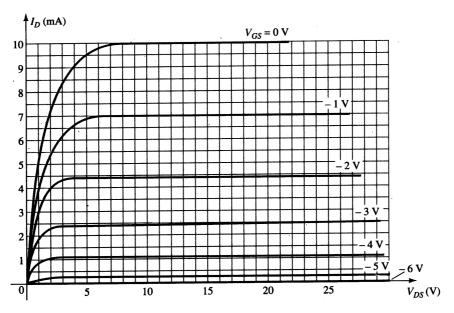

A tensão da porta para a fonte, denotada por  $V_{GS}$ , é a tensão controladora do JFET. Assim como várias curvas para  $I_C$  versus  $V_{CE}$  foram estabelecidas para diferentes níveis de  $I_B$  no TBJ, curvas de  $I_D$  versus  $V_{DS}$  para vários níveis de  $V_{GS}$  podem ser desenvolvidas para o JFET. Para o dispositivo de canal n, a tensão controladora  $V_{GS}$  é feita cada vez mais negativa, a partir de  $V_{GS}$  = 0 V. Ou seja, o terminal de porta estará cada vez mais em potenciais menores comparados à fonte.

Na Fig. 5.9, uma tensão negativa de -1 V foi aplicada entre os terminais de porta e fonte, para uma tensão  $V_{DS}$  reduzida. A polarização negativa estabelece regiões de depleção semelhantes àquelas obtidas com  $V_{GS}=0$  V, mas com níveis menores de  $V_{DS}$ . Portanto, o resultado da aplicação de uma polarização negativa na porta é alcançar a condição de saturação em níveis menores de tensão  $V_{DS}$ , como mostrado na Fig. 5.10, para  $V_{GS}=-1$  V. O nível de saturação resultante para  $I_D$  foi reduzido, e de fato continuará a reduzir para valores de  $V_{GS}$  cada vez mais negativos. Observe também na Fig. 5.10 como a tensão de pinchoff diminui, descrevendo uma parábola, à medida que  $V_{GS}$  se tor-

Fig. 5.9 Aplicação de uma tensão negativa no terminal de porta de um JFET.

na cada vez mais negativo. Eventualmente, quado  $V_{GS}=-V_p$ , a tensão será suficientemente negativa para estabelecer um nível de saturação com  $I_D=0$  mA, e, para todos os efeitos, pode-se considerar que o dispositivo foi "desligado". Em resumo:

O nível de  $V_{GS}$  que resulta em  $I_D = 0$  mA é definido por  $V_{GS} = V_p$ , com  $V_p$  sendo uma tensão negativa para dispositivos de canal n, e uma tensão positiva para JFETs de canal p.

Na maioria das folhas de especificações, a tensão de pinchoff é especializada como  $V_{GS(off)}$  ao invés de  $V_p$ . A folha de especificações será revista mais tarde, ainda neste capítulo, quando os elementos mais importantes forem introduzidos. A região à direita do lugar geométrico da tensão de pinch-off, na Fig. 5.10, é a região normalmente empregada para amplificadores lineares (amplificadores que não distorcem o sinal aplicado), e é quase sempre referida como corrente constante, saturação, ou região de amplificação linear.

Fig. 5.10 Curvas características do JFET de canal  $n \text{ com } I_{DSS} = 8 \text{ mA e } V_p = -4 \text{ V}.$

# Resistor Controlado à Tensão

A região à esquerda do lugar geométrico da tensão de pinch-off, na Fig. 5.10, é denominada  $\partial hmica$  ou região de resistência controlada à tensão. Nesta região, o JFET pode realmente ser empregado como um resistor variável (talvez para um sistema de controle automático de ganho), cuja resistência é controlada pela tensão porta-fonte aplicada. Observe na Fig. 5.10 que a inclinação de cada curva, e portanto a resistência do dispositivo entre dreno e fonte para  $V_{DS} < V_p$  é função da tensão  $V_{GS}$  aplicada. Quando a tensão  $V_{GS}$  assume valores mais negativos, a inclinação da curva torna-se mais horizontal, correspondendo a um aumento no nível de resistência. A equação abaixo fornece uma boa aproximação para o nível de resistência em termos da tensão  $V_{GS}$  aplicada.

$$r_d = \frac{r_o}{(1 - V_{GS}/V_P)^2} \tag{5.1}$$

onde  $r_o$  é a resistência com  $V_{GS}=0$  V e  $r_d$  a resistência para um valor particular de  $V_{GS}$ .

Para um JFET de canal n, com  $r_o$  igual a  $10 \text{ k}\Omega$  ( $V_{GS} = 0 \text{ V}$ ,  $V_p = -6 \text{ V}$ ),  $r_d$  na Eq. (5.1) vale  $40 \text{ k}\Omega$ , para  $V_{GS} = -3 \text{ V}$ .

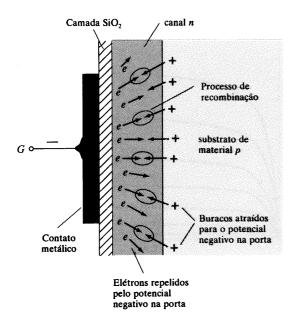

# Dispositivos de Canal p

O JFET de canal p é construído exatamente da mesma forma que o dispositivo de canal n da Fig. 5.2, só que agora as localizações dos materiais tipo p e n são trocadas, como mostrado na Fig. 5.11. Os sentidos das correntes são invertidos, assim como as polaridades das tensões  $V_{GS}$  e  $V_{DS}$ . Para o dispositivo de canal p, o canal será constrito para tensões positivas crescentes da porta para fonte, e para as curvas da Fig. 5.12, os valores de  $V_{DS}$  considerados serão negativos, com  $I_{DSS}$  igual a 6 mA e uma tensão de pinchoff de  $V_{GS} = +6$  V. O sinal menos para  $V_{DS}$  indica simplesmente que a fonte está em um potencial mais alto do que o dreno.

Observe que, para níveis elevados de  $V_{DS}$ , a curva ascende subitamente, assumindo valores ilimitados. O crescimento ver-

Fig. 5.11 JFET de canal p.

**Fig. 5.12** Curvas características para o JFET de canal  $p \text{ com } I_{DSS} = 6 \text{ mA}$  e  $V_p = +6 \text{ V}$

tical é uma indicação de que houve uma ruptura, e a corrente através do canal (no sentido esperado) é limitada agora apenas pelo circuito externo. Embora não apareça na Fig. 5.10, para o dispositivo de canal n, o mesmo ocorre para este tipo de dispositivo se uma tensão suficiente for aplicada. Esta região pode ser evitada se o valor de  $V_{DS_{max}}$  for observado na folha de especificações, e o projeto é tal que o valor de  $V_{DS}$  é menor do que este nível para todos os valores de  $V_{GS}$ .

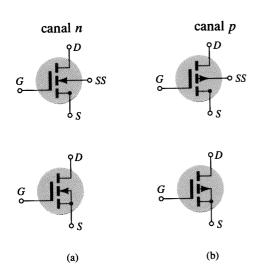

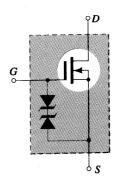

# Símbolos

Os símbolos gráficos para os JFETs de canal n e canal p são mostrados na Fig. 5.13. Observe que a seta está apontando para dentro no dispositivo de canal n da Fig. 5.13a, indicando o sentido que a corrente  $I_G$  iria fluir se a junção p-n fosse diretamente polarizada. Para o dispositivo de canal p (Fig. 5.13b), a única diferença no símbolo é o sentido da seta.

# Sumário

Vários parâmetros e relações importantes foram introduzidos nesta seção. A lista abaixo relaciona alguns que irão surgir freqüentemente na análise feita neste capítulo, e no próximo, para os JFETs de canal *n*.

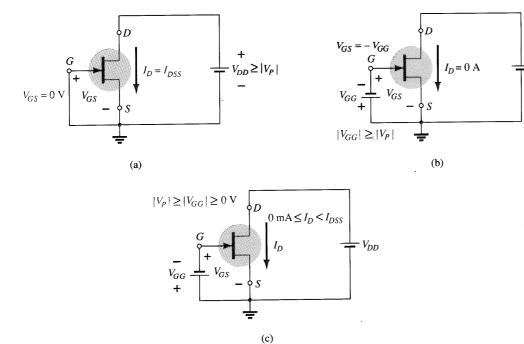

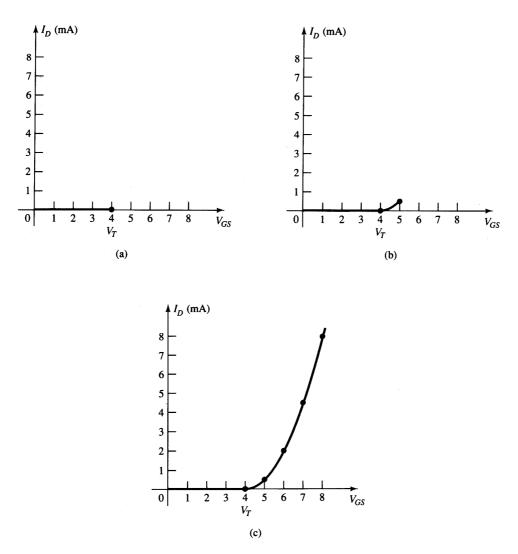

A corrente máxima é definida por  $I_{DSS}$ , e ocorre quando  $V_{GS}$ = 0 V e  $V_{DS} \ge |V_p|$  como mostrado na Fig. 5.14a.

**Fig. 5.13** Símbolos do JFET: (a) canal n; (b) canal p.

**Fig. 5.14** (a)  $V_{GS} = 0$  V,  $I_D = I_{DSS}$ ; (b) corte ( $I_D = 0$  A)  $V_{GS}$  menor do que o nível de pinch-off; (c)  $I_D$  varia entre 0 A e  $I_{DSS}$  para  $V_{GS}$  menor ou igual a 0 V, e maior do que a tensão de pinch-off.

Para tensões  $V_{GS}$  entre porta e fonte menores do que (mais negativos do que) o nível de pinch-off, a corrente de dreno é 0 A ( $I_D=0$  A), como aparece na Fig. 5.14b.

Para todos os valores de  $V_{GS}$  entre 0 V e o nível de pinchoff, a corrente  $I_D$  irá variar entre  $I_{DSS}$  e 0 A, respectivamente, como se pode observar na Fig. 5.14c.

Para os JFETs de canal p, uma lista semelhante pode ser desenvolvida.

# 5.3 CARACTERÍSTICAS DE TRANSFERÊNCIA

# Dedução

Para o TBJ, a corrente de saída  $I_C$  e a corrente controladora de entrada  $I_B$  foram relacionadas pelo parâmetro beta, considerado constante na análise realizada. Na forma de equação,

variável controle

$$I_C = f(I_B) = \beta I_B$$

constante

$$(5.2)$$

Na Eq. (5.2) há uma relação linear entre  $I_C$  e  $I_B$ . Se o valor de  $I_B$  for dobrado,  $I_C$  aumentará também por um fator de 2.

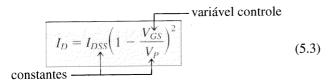

Infelizmente, esta relação linear não existe entre as quantidades de saída e entrada de um JFET. A relação entre  $I_D$  e  $V_{GS}$  é definida pela equação de Shockley:

O termo quadrático da equação resulta em uma relação não-linear entre  $I_D$  e  $V_{GS}$ , produzindo uma curva que cresce exponencialmente com valores crescentes de  $V_{GS}$ .

Para a análise de a ser feita no Cap. 6, o método gráfico será mais direto e fácil de se utilizar do que o método matemático. O método gráfico, entretanto, exigirá o traçado da Eq. (5.3) para representar o dispositivo, e o traçado da equação do circuito relacionando as mesmas variáveis. A solução é definida pelo ponto de interseção das duas curvas. Note que, quando aplicamos o método gráfico, as características do dispositivo não são afetadas pelo circuito no qual o dispositivo é empregado. A equação do circuito pode mudar com a interseção entre as duas curvas, mas a curva de transferência definida pela Eq. (5.3) não é afetada. Em geral, portanto:

As características de transferência definidas pela equação de Shockley não são afetadas pelo circuito no qual o dispositivo é empregado.

A curva de transferência pode ser obtida utilizando-se a equação de Shockley, ou das curvas características da Fig. 5.10. Na Fig. 5.15 são fornecidos dois gráficos com a escala vertical em

William Bradford Shockley (1910-1989), co-inventor do primeiro transistor e formulador da teoria "efeito de campo" empregada no desenvolvimento do transistor e FET. (Cortesia da AT&T Archives.)

Fig. 5.15 Obtendo a curva de transferência das curvas de dreno.

miliampères para cada gráfico. Um é o gráfico de  $I_D$  versus  $V_{DS}$ , enquanto que o outro é  $I_D$  versus  $V_{GS}$ . Utilizando-se as características de dreno à direita do eixo "y", pode ser desenhada uma linha horizontal da região de saturação da curva, denotada por  $V_{GS}=0$  V, ao eixo  $I_D$ . O nível de corrente resultante para ambos os gráficos é  $I_{DSS}$ . O ponto de interseção na curva de  $I_D$  versus  $V_{GS}$  será da maneira mostrada, uma vez que o eixo vertical é definido por  $V_{GS}=0$  V.

Para revisão:

Quando

$$V_{GS} = 0 V$$

,  $I_D = I_{DSS}$ .

Quando  $V_{GS} = V_p = -4$  V, a corrente de dreno é zero miliampères, definindo outro ponto na curva de transferência. Ou seja:

Quando

$$V_{GS} = V_p$$

,  $I_D = 0$  mA.

Antes de prosseguirmos, é importante perceber que as curvas características de dreno relacionam um parâmetro de saída (ou dreno) com outro parâmetro de saída (ou dreno) — ambos os eixos são definidos por variáveis na mesma região das curvas características do dispositivo. As curvas características de transferência relacionam uma corrente de saída (ou dreno) versus um parâmetro controlador de entrada. Há, portanto, uma "transferência" direta das variáveis de entrada para a saída, quando se emprega a curva à esquerda da Fig. 5.15. Se a relação fosse linear, o gráfico de  $I_D$  versus  $V_{GS}$  seria uma reta entre  $I_{DSS}$  e  $V_p$ . Entretanto, a curva é parabólica, já que os intervalos verticais entre as curvas características de dreno diminuem consideravelmente, na medida em que  $V_{GS}$  assume valores mais negativos. Compare o intervalo entre as curvas de  $V_{GS} = 0$  V e  $V_{GS} = -1$  V com o existente entre  $V_{GS} = -3$  V e a tensão de pinch-off. A variação de  $V_{GS}$  é a mesma, mas a variação resultante em  $I_D$  é consideravelmente diversa.

Se uma linha horizontal for desenhada da curva  $V_{GS}=-1~\rm V$  para o eixo  $I_D$ , e então estendida até o outro eixo, pode-se obter outro ponto da curva de transferência. Observe que  $V_{GS}=-1~\rm V$  no eixo das abscissas do gráfico da curva de transferência, para  $I_D=4,5~\rm mA$ . Observe na definição de  $I_D$ , em  $V_{GS}=0~\rm V~e-1~V$ , que os níveis de saturação de  $I_D$  são empregados, e a região ôhmica é ignorada. Continuando com  $V_{GS}=-2~\rm V~e-3~V$ , a curva de transferência pode agora ser completada. Para a análise do Cap. 6, nos basearemos na curva de transferência de  $I_D$  versus  $V_{GS}$ , e não nas características de dreno da Fig. 5.15. Os próximos parágrafos introduzirão um método rápido e eficiente para o traça-

do de  $I_D$  versus  $V_{GS}$ , dados apenas os níveis de  $I_{DSS}$ ,  $V_p$  e a equação de Shockley.

# Aplicando a Equação de Shockley

A curva de transferência da Fig. 5.15 também pode ser obtida diretamente da equação de Shockley (5.3), fornecidos apenas os valores de  $I_{DSS}$  e  $V_p$ . Os níveis de  $I_{DSS}$  e  $V_p$  definem os limites da curva em ambos os eixos, restando-nos apenas achar alguns pontos intermediários. A utilização da Eq. (5.3) como base para o levantamento da curva de transferência da Fig. 5.15 é mais bem demonstrada examinando-se alguns valores específicos de uma variável, e achando o valor resultante para a outra variável, tal como mostrado abaixo:

Substituindo  $V_{GS} = 0$  V dá

Eq. (5.3):

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

$$= I_{DSS} \left( 1 - \frac{0}{V_P} \right)^2 = I_{DSS} (1 - 0)^2$$

$$I_D = I_{DSS}|_{V_{GS} = 0 \text{ V}}$$

(5.4)

Substituindo  $V_{GS} = V_p$  aparece

$$I_{D} = I_{DSS} \left( 1 - \frac{V_{P}}{V_{P}} \right)^{2}$$

$$= I_{DSS} (1 - 1)^{2} = I_{DSS} (0) .$$

$$I_{D} = 0 \text{ A}|_{V_{GS} = V_{P}}$$

(5.5)

Para as características de dreno da Fig. 5.15, se substituirmos  $V_{GS} = -1 \text{ V}$ ,

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

$$= 8 \text{ mA} \left( 1 - \frac{-1 \text{ V}}{-4 \text{ V}} \right)^2 = 8 \text{ mA} \left( 1 - \frac{1}{4} \right)^2 = 8 \text{ mA} (0,75)^2$$

$$= 8 \text{ mA} (0,5625)$$

$$= 4,5 \text{ mA}$$

como mostrado na Fig. 5.15. Observe o cuidado que tivemos com os sinais negativos de  $V_{GS}$  e  $V_p$  nos cálculos acima. A troca de um sinal levaria a um resultado totalmente errado.

Deve ficar bem claro da consideração acima que dados  $I_{DSS}$  e  $V_p$  (normalmente fornecidos pelas folhas de especificações), o valor de  $I_D$  pode ser determinado para qualquer nível de  $V_{GS}$ . Inversamente, utilizando uma álgebra básica, podemos obter [da Eq. (5.3)] uma equação para o nível resultante de  $V_{GS}$  para um dado valor de  $I_D$ . A dedução é bem simples e resulta em

$$V_{GS} = V_P \left( 1 - \sqrt{\frac{I_D}{I_{DSS}}} \right) \tag{5.6}$$

Vamos testar a Eq. (5.6), achando o valor de  $V_{GS}$  que resulta em uma corrente de dreno de 4,5 mA, para o dispositivo com as características mostradas no gráfico da Fig. 5.15.

$$V_{GS} = -4 \text{ V} \left( 1 - \sqrt{\frac{4.5 \text{ mA}}{8 \text{ mA}}} \right)$$

$$= -4 \text{ V} \left( 1 - \sqrt{0.5625} \right) = -4 \text{ V} (1 - 0.75)$$

$$= -4 \text{ V} (0.25)$$

$$= -1 \text{ V}$$

valor substituído no cálculo anterior e verificado pela Fig. 5.15.

# Método Simplificado

e

Uma vez que a curva de transferência é traçada freqüentemente, seria bem vantajoso possuirmos um método simplificado para o levantamento da curva que realizasse o trabalho de modo mais rápido e eficiente e mantivesse ainda um nível aceitável de precisão. O formato da Eq. (5.3) é tal que, para valores específicos de  $V_{GS}$ , os níveis resultantes de  $I_D$  podem ser empregados facilmente na marcação de pontos no gráfico, necessários para o esboço da curva. Se especificarmos  $V_{GS}$  como sendo metade do valor de pinch-off  $V_p$ , o nível resultante de  $I_D$  será o seguinte, determinado pela equação de Shockley:

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

$$= I_{DSS} \left( 1 - \frac{V_{P}/2}{V_P} \right)^2 = I_{DSS} \left( 1 - \frac{1}{2} \right)^2 = I_{DSS}(0,5)^2$$

$$= I_{DSS}(0,25)$$

$$I_D = \frac{I_{DSS}}{4} \bigg|_{V_{GS} = V_p/2} \tag{5.7}$$

Entretanto, é importante observar que a Eq. (5.7) não vale apenas para um valor particular de  $V_p$ . Ela é uma equação geral, para qualquer valor de  $V_p$ , como, por exemplo,  $V_{GS} = V_p/2$ . O resultado determina que a corrente de dreno será sempre um quarto do nível de saturação  $I_{DSS}$ , assim como a tensão porta-fonte é a metade do valor de pinch-off. Observe o valor de  $I_D$  para  $V_{GS} = V_p/2 = -4$  V/2 = -2 V, na Fig. 5.15.

Se fizermos  $I_D = I_{DSS}/2$  e inserirmos na Eq. (5.6), acharemos que

$$V_{GS} = V_P \left( 1 - \sqrt{\frac{I_D}{I_{DSS}}} \right)$$

$$= V_P \left( 1 - \sqrt{\frac{I_{DSS}/2}{I_{DSS}}} \right) = V_P (1 - \sqrt{0.5}) = V_P (0.293)$$

$$V_{GS} \approx 0.3 V_P |_{I_D = I_{DS}/2}$$

(5.8)

Pontos adicionais podem ser determinados, mas a curva de transferência pode ser esboçada com um nível satisfatório de precisão, utilizando-se apenas os quatro pontos definidos acima, e revistos no Quadro 5.1. De fato, na análise do Cap. 6, um máximo de quatro pontos são utilizados para o esboço das curvas de transferência. Na maioria das situações, utilizando apenas o ponto definido por  $V_{GS} = V_p/2$  e as interseções dos eixos em  $I_{DSS}$  e  $V_n$ , será o suficiente para grande parte dos cálculos.

QUADRO 5.1  $V_{GS}$  versus  $I_D$  Usando a Equação de Shockley

| $V_{GS}$                                                     | $I_D$                                         |

|--------------------------------------------------------------|-----------------------------------------------|

| 0                                                            | $I_{DSS}$                                     |

| $\begin{array}{c} 0.3 \ V_p \\ 0.5 \ V_p \\ V_p \end{array}$ | $I_{DSS}$ $I_{DSS}/2$ $I_{DSS}/4$ $0~{ m mA}$ |

| 0,5 V <sub>p</sub>                                           | $I_{DSS}/4$                                   |

| $V_p$                                                        | 0 mA                                          |

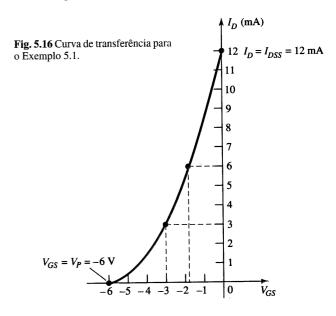

# EXEMPLO 5.1

Esboce a curva de transferência definida por  $I_{DSS} = 12 \text{ mA e } V_p = -6 \text{ V}.$

# Solução

Os dois pontos são definidos por

$$I_{DSS} = \mathbf{12} \ \mathbf{mA} \ \mathbf{e} \ V_{GS} = \mathbf{0} \ \mathbf{V}$$

$$I_D = \mathbf{0} \ \mathbf{mA} \ \mathbf{e} \ V_{GS} = V_p$$

Em  $V_{GS} = V_p/2 = -6 \text{ V}/2 = -3 \text{ V}$ , a corrente de dreno será determinada por  $I_D = I_{DSS}/4 = 12 \text{ mA}/4 = 3 \text{ mA}$ . Em  $I_D = I_{DSS}/2 = 12 \text{ mA}/4 = 2 \text{ mA}$ , a tensão porta-fonte é determinada por  $V_{GS} \cong 0.3 \text{ V}_p = 0.3(-6 \text{ V}) = -1.8 \text{ V}$ . Todos os quatro pontos do gráfico estão bem definidos na Fig. 5.16, com a curva de transferência completa.

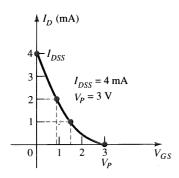

Para os dispositivos de canal p, a equação de Shockley (5.3) pode, ainda, ser aplicada exatamente como mostrada. Neste caso, tanto  $V_p$  como  $V_{GS}$  serão positivos e a curva será a curva de transferência refletida do dispositivo de canal n, com os mesmos valores limitantes.

### EXEMPLO 5.2

Esboce a curva de transferência para um dispositivo de canal p, com  $I_{DSS} = 4$  mA e  $V_p = 3$  V.

# Solução

Em  $V_{GS} = V_p/2 = 3 \text{ V}/2 = 1,5 \text{ V}, I_D = I_{DSS}/4 = 4 \text{ mA}/4 = 1 \text{ mA}.$ Em  $I_D = I_{DSS}/2 = 4 \text{ mA}/2 = 2 \text{ mA}, V_{GS} = 0,3 V_p = 0,3(3 \text{ V}) = 0,9 \text{ V}.$  Todos estes pontos aparecem na Fig. 5.17, junto com os pontos definidos por  $I_{DSS}$  e  $V_p$ .

Fig. 5.17 Curva de transferência para o dispositivo de canal p do Exemplo 5.2.

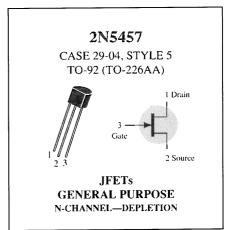

# 5.4 FOLHA DE ESPECIFICAÇÕES (JFETs)

Embora o conteúdo geral das folhas de especificações possa variar desde o mínimo absoluto até um grande número de quadros e gráficos, existem alguns parâmetros fundamentais que serão fornecidos por todos os fabricantes. Alguns dos mais importantes serão apresentados nos próximos parágrafos. A folha de especificação para o JFET 2N5457 de canal n, fabricado pela Motorola, é mostrado na Fig. 5.18.

# Especificações Máximas Nominais

A lista contendo os níveis máximos permitidos para um dispositivo normalmente aparece no início das folhas de especificações, com as tensões máximas entre os terminais, níveis máximos de corrente, e nível máximo de dissipação de proteína do dispositivo. Os níveis máximos específicos para  $V_{DS}$  e  $V_{DG}$  não devem ser ultrapassados, em qualquer ponto de operação determinado no projeto. A fonte aplicada  $V_{DD}$  pode exceder estes valores, mas a tensão existente entre estes terminais não deve nunca ultrapassálos. Qualquer projeto tentará evitar estes níveis, mantendo uma boa margem de segurança. O termo reverso em  $V_{GSR}$  define a tensão máxima positiva em relação ao terminal de porta (conside-

rando a polarização para um dispositivo de canal n), antes de atingir a tensão de ruptura. Em algumas folhas de especificações, é denominada de  $BV_{DSS}$ — Tensão de Ruptura com Dreno-Fonte em Curto ( $V_{DS}=0$  V). Embora normalmente projetado para operar com  $I_G=0$  mA, se forçado a aceitar uma corrente de porta, o dispositivo pode suportar até 10 mA sem ser danificado. A dissipação total do dispositivo em  $25^{\circ}$ C (temperatura ambiente) é a potência máxima que ele pode dissipar sob condições normais de operação, e é definida por

$$P_D = V_{DS}I_D \tag{5.9}$$

Observe a semelhança no formato com a equação de dissipação máxima de potência para o TBJ.

O fator de redução é discutido com detalhes no Cap. 3, mas, por ora, saiba que a especificação 2,82 mW/°C revela que a dissipação máxima *diminui* de 2,82 mW para cada *aumento* de 1°C na temperatura, acima de 25°C.

# Características Elétricas

As características elétricas incluem o nível de  $V_p$  nas CARACTERÍSTICAS QUANDO NÃO CONDUZINDO e  $I_{DSS}$  nas CARACTERÍSTICAS QUANDO CONDUZINDO. Neste caso,  $V_p = V_{GS(off)}$  varia de -0.5 até -6.0 V, e  $I_{DSS}$  de 1 até 5 mA. O fato de ambos os parâmetros variarem de dispositivo para dispositivo deve ser considerado no desenvolvimento de um projeto. As outras quantidades são definidas sob as condições mostradas entre parênteses. As características de pequenos sinais são discutidas no Cap. 9.

# Fabricação do Encapsulamento e Identificação dos Terminais

Este particular JFET tem o aspecto mostrado na folha de especificações da Fig. 5.18. A identificação dos terminais é igualmente fornecida da figura. Os JFETs estão disponíveis ainda em encapsulamento tipo caneca, como mostrado na Fig. 5.19, com a identificação dos seus terminais.

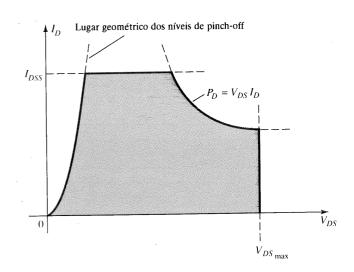

# Região de Operação

A folha de especificações e a curva definida pelas tensões de pinch-off para cada nível de  $V_{GS}$  determinam a região de operação nas curvas de dreno da Fig. 5.20, para uma amplificação linear. A região ôhmica define os valores mínimos permitidos de  $V_{DS}$ , para cada nível de  $V_{GS}$ , e  $V_{DS_{max}}$  especifica o valor máximo deste parâmetro. A corrente de saturação  $I_{DSS}$ , corrente máxima de dreno, e o nível máximo de dissipação de potência definem a curva desenhada, como foi feito para o TBJ. A região sombreada resultante é a região de operação normalmente utilizada em um projeto de amplificador.

# 5.5 INSTRUMENTAÇÃO

Lembre do Cap. 3 que existem instrumentos de medida disponíveis para medir o valor de  $\beta_{dc}$  para o TBJ. O mesmo não se pode dizer para o FET, já que não há dispositivos semelhantes para medir os níveis de  $I_{DSS}$  e  $V_p$ . Entretanto, o traçador de curvas in-

### MAXIMUM RATINGS

| Rating                                                             | Symbol           | Value       | Unit        |

|--------------------------------------------------------------------|------------------|-------------|-------------|

| Drain-Source Voltage                                               | V <sub>DS</sub>  | 25          | Vdc         |

| Drain-Gate Voltage                                                 | V <sub>DG</sub>  | 25          | Vdc         |

| Reverse Gate-Source Voltage                                        | V <sub>GSR</sub> | -25         | Vdc         |

| Gate Current                                                       | $I_G$            | 10          | mAdc        |

| Total Device Dissipation @ T <sub>A</sub> = 25°C Derate above 25°C | P <sub>D</sub>   | 310<br>2.82 | mW<br>mW/°C |

| Junction Temperature Range                                         | Тј               | 125         | °C          |

| Storage Channel Temperature Range                                  | T <sub>stg</sub> | -65 to +150 | °C          |

Refer to 2N4220 for graphs.

| ELECTRICAL | CHARACTERISTICS | $(T_A = 25^{\circ}C \text{ un})$ | less otherwise noted) |

|------------|-----------------|----------------------------------|-----------------------|

|            |                 |                                  |                       |

| Characteristic                                                                                                                          |                      | Min  | Тур  | Max          | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|------|--------------|------|

| OFF CHARACTERISTICS  Gate-Source Breakdown Voltage (I <sub>G</sub> = -10 μAdc, V <sub>DS</sub> = 0)                                     | V <sub>(BR)GSS</sub> | -25  | _    | _            | Vdc  |

| Gate Reverse Current<br>$(V_{GS} = -15 \text{ Vdc}, V_{DS} = 0)$<br>$(V_{GS} = -15 \text{ Vdc}, V_{DS} = 0, T_A = 100^{\circ}\text{C})$ | I <sub>GSS</sub>     |      | _    | -1.0<br>-200 | nAde |

| Gate Source Cutoff Voltage $(V_{DS} = 15 \text{ Vdc}, I_D = 10 \text{ nAdc})$ 2N5457                                                    | V <sub>GS(off)</sub> | -0.5 | -    | -6.0         | Vdc  |

| Gate Source Voltage<br>$(V_{DS} = 15 \text{ Vde}, I_D = 100 \mu \text{Ade})$ 2N5457                                                     | $V_{GS}$             | _    | -2.5 | _            | Vdc  |

| ON   | CHAR | RACTE | ERIST            | ics |

|------|------|-------|------------------|-----|

| 17:1 | CHAR |       | 71 <b>4</b> 10 1 |     |

| Zero-Gate-Voltage Drain Current*               | IDSS |     |     |     | mAde |

|------------------------------------------------|------|-----|-----|-----|------|

| $(V_{DS} = 15 \text{ Vdc}, V_{GS} = 0)$ 2N5457 |      | 1.0 | 3.0 | 5.0 |      |

| CMALL | CHENAL | CHARACTERISTICS |  |

|-------|--------|-----------------|--|

| Forward Transfer Admittance Common Source* (V <sub>DS</sub> = 15 Vdc, V <sub>GS</sub> = 0, f = 1.0 kHz) 2N5457 | lyfsl            | 1000 | -   | 5000 | μmhos |

|----------------------------------------------------------------------------------------------------------------|------------------|------|-----|------|-------|

| Output Admittance Common Source*<br>(V <sub>DS</sub> = 15 Vdc, V <sub>GS</sub> = 0, f = 1.0 kHz)               | y <sub>os</sub>  | _    | 10  | 50   | μmhos |

| Input Capacitance $(V_{DS} = 15 \text{ Vdc}, V_{GS} = 0, f = 1.0 \text{ MHz})$                                 | C <sub>iss</sub> | _    | 4.5 | 7.0  | pF    |

| Reverse Transfer Capacitance $(V_{DS} = 15 \text{ Vdc}, V_{GS} = 0, f = 1.0 \text{ MHz})$                      | C <sub>rss</sub> | _    | 1.5 | 3.0  | pF    |

<sup>\*</sup>Pulse Test: Pulse Width ≤ 630 ms; Duty Cycle ≤ 10%

Fig. 5.18 JFET 2N5457 de canal n da Motorola.\*

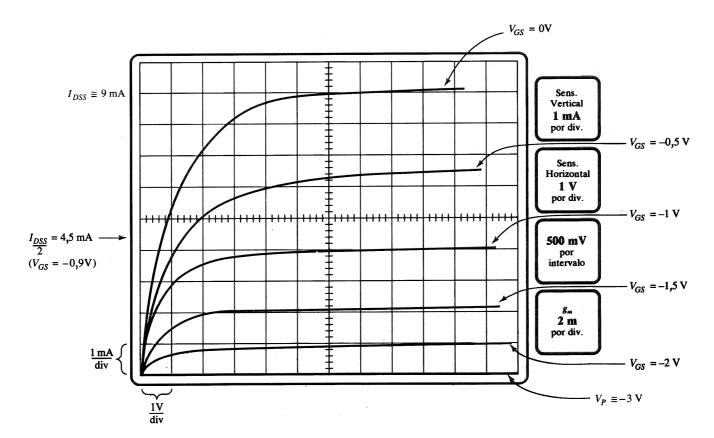

troduzido para o TBJ pode revelar as características de dreno do JFET, por meio de um ajuste apropriado dos diversos controles. A escala vertical (em miliampères) e a escala horizontal (em volts) foram ajustadas para mostrar por inteiro as curvas, como apresentado na Fig. 5.21. Para o JFET da Fig. 5.21, cada divisão vertical (em centímetros) representa uma variação de  $I_C$  de 1 mA, enquanto a divisão horizontal corresponde a 1 V. O intervalo entre os níveis de  $V_{GS}$  é de 500 mV, ou seja, 0,5 V/intervalo, revelando que a curva mais acima é de  $V_{GS}=0$  V e a curva logo abaixo é de  $V_{GS}=-0,5$  V para o dispositivo de canal n. Utilizando o mesmo intervalo, a próxima curva é -1 V, depois -1,5 V, e finalmente -2 V. Desenhando-se uma reta da curva mais acima até o eixo  $I_D$ , o valor de  $I_{DSS}$  pode ser estimado em mais ou menos 9 mA. O nível de  $V_p$  pode ser estimado observando-se o valor de  $V_{GS}$  da curva inferior e levando-se em conta a redução da distância entre as curvas na medida em que  $V_{GS}$  se torna mais

<sup>\*</sup>N.T.: Os termos originais em inglês contidos nesta figura não foram traduzidos porque o que se encontra na prática, no laboratório, são especificações escritas em inglês, com raras exceções. Deseja-se, com isto, que o leitor se acostume aos termos técnicos que ele encontrará na sua vida profissional.

# 2N2844 ENCAPSULAMENTO 22-03, MODELO 12 TO-18 (TO-206AA) Dreno (Encapsulamento) 2 Porta 1 Fonte JFETs de EMPREGO GERAL CANAL-P

**Fig. 5.19** Encapsulamento tipo caneca e identificação dos terminais para um JFET de canal p.

negativo. Neste caso,  $V_p$  é, certamente, mais negativo do que -2 V e talvez próximo a -2.5 V. Entretanto, saiba que as curvas de  $V_{GS}$  estão muito próximas umas das outras quando se aproximam da condição de corte, e talvez  $V_p = -3$  V seja uma melhor opção. Deve-se também observar que o intervalo entre as curvas é ajustado para mostrar um total de cinco curvas, limitando as curvas a  $V_{GS} = 0$  V, -0.5 V, -1 V, -1.5 V, e-2 V. Se fosse para 10 curvas, o incremento seria reduzido para 250 V = 0.25 V, e a curva  $V_{GS} = -2.25$  mV seria incluída, além das demais curvas adicionadas entre as mostradas na Fig. 5.21. A curva  $V_{GS} = -2.25$  V revelaria o quanto as curvas se aproximam umas das outras à

Fig. 5.20 Região de operação para um projeto de amplificação linear.

medida que se aproximam de  $V_p$ . Felizmente, o nível de  $V_p$  pode ser estimado com grau de precisão razoável, aplicando-se simplesmente a condição estabelecida no Quadro 5.1. Ou seja, quando  $I_D=I_{DSS}/2$ , então  $V_{GS}=0,3\ V_p$ . Para as curvas características da Fig. 5.21,  $I_D=I_{DSS}/2=9\ \text{mA}/2=4,5\ \text{mA}$ , e como se pode ver na Fig. 5.21, o valor correspondente de  $V_{GS}$  é aproximadamente  $-0,9\ \text{V}$ . Utilizando esta informação achamos que  $V_p=V_{GS}/0,3=-0,9\ \text{V}/0,3=-3\ \text{V}$ , que será o nível escolhido para

Fig. 5.21 Curvas características de dreno para um JFET 2N4416 apresentadas por um traçador de curvas.

este dispositivo. Com este valor, determinamos que em  $V_{GS} = -2 \text{ V}$ ,

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

$$= 9 \text{ mA} \left( 1 - \frac{-2 \text{ V}}{-3 \text{ V}} \right)^2$$

$$\approx 1 \text{ mA}$$

confirmado pela Fig. 5.21.

Em  $V_{GS} = -2.5$  V, a equação de Shockley produz  $I_D = 0.25$  mA, com  $V_p = -3$  V, revelando claramente o quão rápido as curvas se aproximam de  $V_p$ . A importância do parâmetro  $g_m$  e a forma como ele é determinado das curvas da Fig. 5.21 são abordadas no Cap. 8, quando as condições de pequenos sinais forem examinadas.

# 5.6 RELAÇÕES IMPORTANTES

Várias equações e características de operação relevantes foram introduzidas nas últimas seções, e são de particular importância para a análise que vem a seguir das configurações de e ac. Com o intuito de isolar e enfatizar a importância de tais relações, elas foram repetidas abaixo, ao lado das equações correspondentes para o TBJ. As equações do JFET são definidas para a configuração da Fig. 5.22a, enquanto que as equações do TBJ baseiamse na Fig. 5.22b.

$$JFET \qquad BJT$$

$$I_D = I_{DSS} \left(1 - \frac{V_{GS}}{V_P}\right)^2 \iff I_C = \beta I_B$$

$$I_D = I_S \qquad \iff I_C \cong I_E$$

$$I_G \cong 0 \text{ A} \qquad \iff V_{BE} \cong 0.7 \text{ V}$$

$$(5.10)$$

Uma clara compreensão do que realmente representa cada uma das equações acima é suficiente para abordar a mais complexa das configurações dc. Lembre que  $V_{BE}=0.7\,\mathrm{V}$  era amiúde o ponto de partida para a análise de uma configuração com TBJ. De maneira análoga, a condição  $I_G=0\,\mathrm{A}$  é freqüentemente a informação inicial utilizada para a análise de uma configuração com JFET. Para a configuração com TBJ,  $I_B$  é, em geral, o primeiro parâmetro a ser determinado. Para a JFET é normalmente  $V_{GS}$ . A semelhança entre as análises das configurações com TBJ e JFET se tornará evidente no Cap. 6.

Fig. 5.22 (a) JFET versus (b) TBJ.

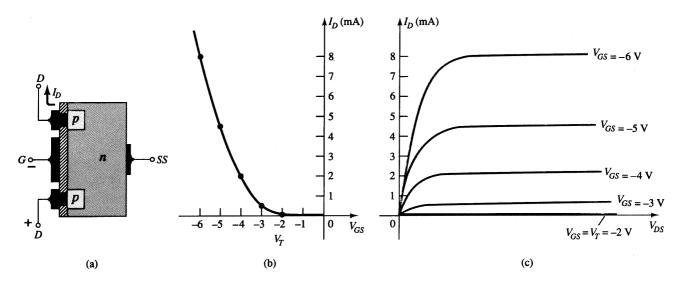

# 5.7 MOSFET TIPO DEPLEÇÃO

Como mencionado na introdução deste capítulo, há dois tipos de FETs: JFETs e MOSFETs. Os MOSFETs subdividem-se em tipo depleção e tipo intensificação. Os termos depleção e intensificação definem os seus modos básicos de operação, enquanto que a expressão MOSFET representa o transistor de efeito de campo metal óxido semicondutor (do inglês, metal-oxide-semiconductor-field-effect transistor). Como existem diferenças nas características e operação dos dois tipos de MOSFET, eles são abordados em seções separadas. Nesta seção, examinaremos o MOSFET tipo depleção, com características semelhantes às de um JFET entre o corte e a saturação de  $I_{DSS}$ ; entretanto, suas curvas características apresentam uma particularidade: estendem-se até a região de polaridade oposta para  $V_{GS}$ .

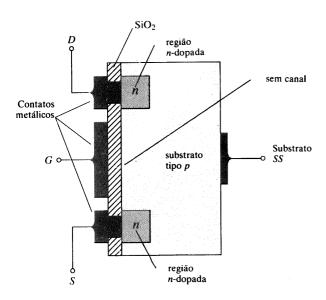

# Construção Básica

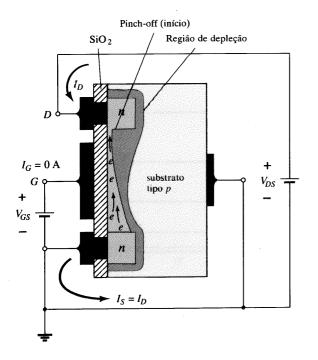

A construção básica do MOSFET tipo depleção de canal n é mostrada na Fig. 5.23. Uma camada grossa de material tipo p é formada a partir de uma base de silício, e é chamada de substrato. Ela representa o alicerce sobre o qual o dispositivo será construído. Em alguns casos, o substrato está internamente conectado ao terminal de fonte. Entretanto, muitos dispositivos discretos oferecem um terminal adicional, denominado SS, resultando em um dispositivo com quatro terminais, como o que aparece na Fig. 5.23. Os terminais de fonte e dreno são conectados por meio de contatos metálicos às regiões n-dopadas, ligadas entre si por um canal n como mostra a figura. A porta é conectada também à superfície metálica de contato, mas permanece isolada do canal n por uma camada muito fina de dióxido de silício ( $SiO_2$ ). O  $SiO_2$ é um tipo particular de isolante, denominado dielétrico, que cria campos elétricos opostos (por esta razão o prefixo di-) quando submetido a um campo externo aplicado. O fato de a camada de SiO<sub>2</sub> representar uma camada isolante, revela o seguinte:

Não há conexão elétrica direta entre o terminal de porta e o canal de um MOSFET.

Fig. 5.23 MOSFET tipo depleção de canal n.

# Além disso:

É a camada isolante de  $SiO_2$  na construção do MOSFET a responsável pela desejável alta impedância de entrada do dispositivo.

Na verdade, a impedância de entrada de um MOSFET equivale normalmente a um JFET típico, ainda que a impedância de entrada da maioria dos JFETs seja bastante alta para grande parte das aplicações. A impedância de entrada extremamente alta continua confirmando o fato de que a corrente de porta  $(I_G)$  é absolutamente zero ampère para as configurações de polarização dc.

A razão para o nome FET metal óxido semicondutor torna-se agora muito óbvia. O *metal* refere-se às conexões de dreno, fonte e porta com superfície apropriada — em particular, o terminal de porta e o controle proporcionado pela área de superfície de contato; o *óxido* para a camada isolante de dióxido de silício; e *semicondutor* para a estrutura básica na qual as regiões tipo *p* e *n* estão espalhadas. A camada isolante entre a porta e o canal sugeriu um outro nome para o dispositivo: *FET de porta isolada* ou *IGFET* (*insulated-gate FET*), ainda que este nome esteja sendo cada vez menos utilizado na atual literatura.

# Operação Básica e Características

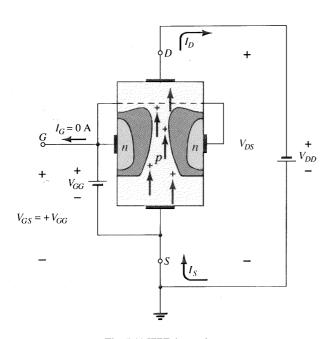

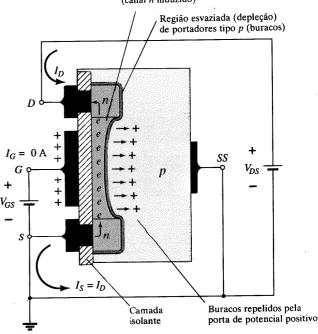

Na Fig. 5.24, a tensão porta-fonte é feita zero volt, devido à conexão de um terminal com o outro, e a tensão  $V_{DS}$  é aplicada através dos terminais dreno-fonte. O resultado é uma atração para o potencial positivo do dreno, dos elétrons *livres* do canal n, estabelecendo uma corrente semelhante à que atravessa o canal do JFET. Na verdade, a corrente resultante com  $V_{GS}=0$  V continua a ser chamada de  $I_{DSS}$ , conforme a Fig. 5.25.

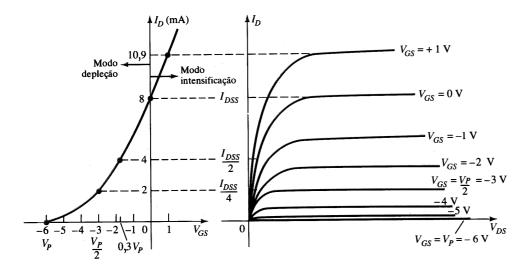

Na Fig. 5.26, a tensão  $V_{GS}$  é negativa, p. ex., -1 V. O potencial negativo na porta tenderá a pressionar os elétrons em direção ao substrato tipo p (cargas do mesmo tipo se repelem), e atrair buracos do substrato tipo p (cargas opostas se atraem), como mostrado na Fig. 5.26. Dependendo da amplitude da polarização negativa estabelecida por  $V_{GS}$ , teremos um nível de recombinação entre elétrons e buracos, reduzindo o número de elétrons livres no canal n disponíveis para a condução. Quanto mais negativa a polarização, maior é a taxa de recombinação. O valor resultante da corrente de dreno é, portanto, reduzido à medida que

Fig. 5.24 MOSFET tipo depleção de canal  $n \text{ com } V_{GS} = 0 \text{ V}$  e uma tensão  $V_{DD}$  aplicada.

$V_{GS}$  se torna mais negativa, como mostra a Fig. 5.25 para  $V_{GS} = -1$  V, -2 V, e assim por diante, até o nível de pinch-off de -6 V. Os níveis resultantes de corrente de dreno e o traçado da curva de transferência são levantados exatamente da maneira descrita para o JFET.

Para valores positivos de  $V_{GS}$ , a porta, agora com potencial positivo, arrasta elétrons adicionais (portadores livres) do substrato tipo p devido à corrente de fuga reversa, e estabelece novos portadores através de colisões resultantes de partículas aceleradas. Se a tensão porta-fonte continuar a crescer positivamente, a Fig. 5.25 mostra que a corrente de dreno crescerá rápido pelas razões listadas acima. O espaçamento vertical entre as curvas  $V_{GS} = 0 \text{ V e } V_{GS} = +1 \text{ V da Fig. 5.25 \'e}$  uma clara indicação do quanto a corrente aumenta quando se varia  $V_{GS}$  de 1 volt. Devido à acentuada elevação da curva, o projetista deve se preocupar com a especificação para a máxima corrente de dreno, uma vez que ela pode ser ultrapassada com uma tensão positiva de porta. Ou

Fig. 5.25 Características de dreno e transferência para um MOSFET tipo depleção de canal n.

Fig. 5.26 Redução dos portadores livres no canal devido ao potencial negativo no terminal de porta.

seja, para o dispositivo da Fig. 5.25, a aplicação de uma tensão  $V_{GS} = +4$  V resultaria em uma corrente de dreno de 22,2 mA, capaz de eventualmente exceder a especificação máxima (de corrente ou potência) para o dispositivo. Como revelado acima, a aplicação de uma tensão positiva porta-fonte "intensificou" o número de portadores livres no canal, comparado ao estabelecido quando  $V_{GS} = 0$  V. Por isso, a região de tensões positivas de porta, nas curvas de dreno ou de transferência, é normalmente chamada região de intensificação, e a região entre os níveis de corte e saturação é denominada região de depleção.

É particularmente interessante e útil que a equação de Shockley seja aplicável às características do MOSFET tipo depleção, nas regiões de depleção e intensificação. Para ambas as regiões, deve-se apenas tomar cuidado com o sinal de  $V_{GS}$  e atenção nas operações matemáticas.

# EXEMPLO 5.3

Esboce a curva de transferência para um MOSFET tipo depleção de canal  $n \text{ com } I_{DSS} = 10 \text{ mA e } Vp = -4 \text{ V}.$

# Solução

Em

$$V_{GS} = 0 \text{ V}, \quad I_D = I_{DSS} = 10 \text{ mA}$$

$V_{GS} = V_P = -4 \text{ V}, \quad I_D = 0 \text{ mA}$   $V_{GS} = \frac{V_P}{2} = \frac{-4 \text{ V}}{2} = -2 \text{ V}, \quad I_D = \frac{I_{DSS}}{4} = \frac{10 \text{ mA}}{4} = 2,5 \text{ mA}$  e em  $I_D = \frac{I_{DSS}}{2}, \quad V_{GS} = 0,3V_P = 0,3(-4 \text{ V}) = -1,2 \text{ V}$

que pode ser visualizado na Fig. 5.27.

**Fig. 5.27** Curva de transferência para um MOSFET tipo depleção de canal n com  $I_{\rm DSS}=10$  mA e  $V_p=-4$  V.

Antes de traçar a região para valores positivos de  $V_{GS}$ , observe que  $I_D$  aumenta muito rapidamente para valores positivos crescentes de  $V_{GS}$ . Portanto, escolha valores razoáveis para se substituir na equação de Shockley. Neste caso, tentaremos +1 V:

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

$$= 10 \text{ mA} \left( 1 - \frac{+1 \text{ V}}{-4 \text{ V}} \right)^2 = 10 \text{ mA} (1 + 0.25)^2 =$$

$$= 10 \text{ mA} (1.5625)$$

$$\approx 15.63 \text{ mA}$$

que é suficientemente alto para completar o gráfico.

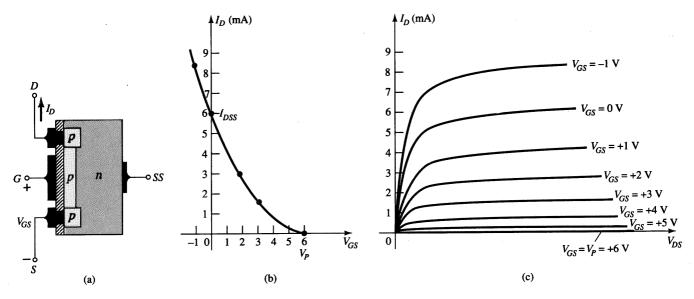

# MOSFET Tipo Depleção de Canal p

A construção de MOSFET tipo depleção de canal p é exatamente oposta ao que aparece na Fig. 5.23. Isto é, existe agora um substrato tipo n e um canal tipo p, como mostrado na Fig. 5.28a. Os terminais são os mesmos, mas todas as polaridades das tensões e os sentidos da correntes são invertidos, como mostrado na mesma figura. As curvas de dreno possuem o mesmo formato das curvas apresentadas na Fig. 5.25, porém com valores negativos de  $V_{DS}$ , positivos de  $I_D$  (uma vez que o sentido definido foi

Fig. 5.28 MOSFET tipo depleção de canal  $p \text{ com } I_{DSS} = 6 \text{ mA e } V_p = +6 \text{ V}.$

invertido), e  $V_{GS}$  com polaridades opostas, como se pode observar na Fig. 5.28c. A inversão da polaridade de  $V_{GS}$  resulta em uma curva de transferência com o mesmo formato da anterior, porém refletida em relação ao eixo  $I_D$ , como mostra a Fig. 5.28b. Ou seja, a corrente de dreno irá do corte, em  $V_{GS} = V_p$  na região positiva de  $V_{GS}$ , até  $I_{DSS}$ , e continuará a aumentar para valores cada vez mais negativos de  $V_{GS}$ . A equação de Shockley é ainda aplicável, e requer apenas que se utilize o sinal correto de  $V_{GS}$  e  $V_p$  na equação.

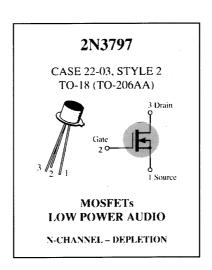

# Símbolos, Folhas de Especificações e Encapsulamento

Os símbolos gráficos de um MOSFET tipo depleção de canal n e p são apresentados na Fig. 5.29. Observe que os símbolos escolhidos tentam refletir a construção real do dispositivo. A au-

**Fig. 5.29** Símbolos gráficos para (a) MOSFETs tipo depleção de canal n e (b) MOSFETs tipo depleção de canal p.

sência de uma conexão direta (devido à isolação da porta) entre a porta e o canal é representada por um espaço entre a porta e os outros terminais do símbolo. A linha vertical que representa o canal liga o dreno à fonte e é "sustentada" pelo substrato. São reservados dois símbolos para cada tipo de canal, isto porque, em alguns dispositivos, o substrato tem um terminal externo, enquanto que em outros não. Em grande parte da análise realizada no Cap. 6, serão utilizados dispositivos com o substrato e a fonte conectados, sendo utilizados, portanto, os símbolos inferiores da Fig. 5.29.

O dispositivo que aparece na Fig. 5.30 possui três terminais, e a identificação destes é mostrada na mesma figura. A folha de especificações para um MOSFET tipo depleção é semelhante à de um JFET. Os níveis de  $V_p$  e  $I_{DSS}$  são fornecidos ao longo da lista, com os valores máximos permitidos e as características para o estado "ligado" e "desligado". Além disso, já que  $I_D$  pode ultrapassar o nível  $I_{DSS}$ , normalmente se fornece outro ponto que representa um valor típico de  $I_D$  para uma tensão positiva (quando o dispositivo é de canal n). Para o exemplo da Fig. 5.30,  $I_D$  é  $I_{D(0n)} = 9$  mA dc com  $V_{DS} = 10$  V e  $V_{GS} = 3,5$  V.

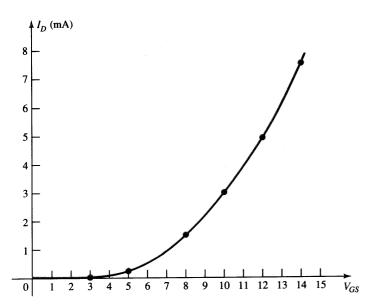

# 5.8 MOSFET TIPO INTENSIFICAÇÃO

Embora existam algumas semelhanças na construção e no modo de operação entre o MOSFET tipo depleção e tipo intensificação, as características do MOSFET tipo intensificação apresentam muitas particularidades. A curva de transferência não é definida pela equação de Shockley, e a corrente de dreno, para este dispositivo, é cortada antes da tensão porta-fonte atingir determinado valor. Em particular, o controle da corrente neste dispositivo de canal n é realizado por uma tensão positiva porta-fonte, o que não ocorria para o JFET de canal n e MOSFET tipo depleção de canal n, onde este controle era feito por tensões negativas.

# Construção Básica

A construção básica de um MOSFET tipo intensificação de canal n é apresentada na Fig. 5.31. Uma camada grossa de material tipo p é formada a partir de uma base de silício, e é novamente

## MAXIMUM RATINGS

Drain-Gate Reverse Current (1)  $(V_{DG} = 10 \text{ V}, I_S = 0)$

| Rating                                                             | Symbol          | Value       | Unit        |  |

|--------------------------------------------------------------------|-----------------|-------------|-------------|--|

| Drain-Source Voltage 2N3797                                        | V <sub>DS</sub> | 20          | Vdc         |  |

| Gate -Source Voltage                                               | $V_{GS}$        | ±10         | Vdc         |  |

| Drain Current                                                      | ID              | 20          | mAdc        |  |

| Total Device Dissipation @ T <sub>A</sub> = 25°C Derate above 25°C | P <sub>D</sub>  | 200<br>1.14 | mW<br>mW/°C |  |

| Junction Temperature Range                                         | Τ,              | +175        | (,          |  |

| Storage Channel Temperature Range                                  | Tstg            | 65 to +200  | C           |  |

| Characteristic                                                                                                                    | Symbol               | Min | Тур | Max        | Unit |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|-----|------------|------|--|--|

| OFF CHARACTERISTICS                                                                                                               |                      |     |     |            |      |  |  |

| Drain Source Breakdown Voltage ( $V_{GS} = 7.0 \text{ V}, I_D = 5.0 \mu\text{A}$ ) 2N3797                                         | V <sub>(BR)DSX</sub> | 20  | 25  |            | Vdc  |  |  |

| Gate Reverse Current (1)<br>$(V_{GS} = -10 \text{ V}, V_{DS} = 0)$<br>$(V_{GS} = -10 \text{ V}, V_{DS} = 0, T_A = 150 \text{ C})$ | I <sub>GSS</sub>     |     |     | 1.0<br>200 | pAdc |  |  |

| Gate Source Cutoff Voltage $(I_D=2.0~\mu\text{A}, V_{DS}=10~\text{V})$ 2N3797                                                     | V <sub>GS(off)</sub> | +   | 5.0 | -7.0       | Vdc  |  |  |

| ON CHARACTERISTICS                                                           |                    |     |     |     |      |

|------------------------------------------------------------------------------|--------------------|-----|-----|-----|------|

| Zero-Gate-Voltage Drain Current $(V_{DS} = 10 \text{ V}, V_{GS} = 0)$ 2N3797 | I <sub>DSS</sub>   | 2.0 | 2.9 | 6.0 | mAdc |

| On-State Drain Current<br>(Vps = 10 V, V <sub>GS</sub> = +3.5 V)             | I <sub>D(on)</sub> |     |     |     | mAdc |

| SMALL-SIGNAL CHARACTERISTICS                                                                 |        |            | ·    | ,    |      |       |

|----------------------------------------------------------------------------------------------|--------|------------|------|------|------|-------|

| Forward Transfer Admittance $(V_{DS} = 10 \text{ V}, V_{GS} = 0, f = 1.0 \text{ kHz})$       | 2N3797 | $ Y_{ts} $ | 1500 | 2300 | 3000 | μmhos |

| $(V_{DS} = 10 \text{ V}, V_{GS} = 0, f = 1.0 \text{ MHz})$                                   | 2N3797 |            | 1500 |      |      |       |

| Output Admittance $(I_{DS} = 10 \text{ V}, \text{ V}_{GS} = 0, \text{ f} = 1.0 \text{ kHz})$ | 2N3797 | Yos        |      | 27   | 60   | μmhos |

| Input Capacitance $(V_{DS}=10~V, V_{GS}=0, f=1.0~MHz)$                                       | 2N3797 | Ciss       |      | 6,0  | 8.0  | bĿ    |

| Reverse Transfer Capacitance<br>$(V_{DS} = 10 \text{ V}, V_{GS} = 0, f = 1, 0 \text{ MHz})$  |        | Crss       |      | 0.5  | 0.8  | bl:   |

| ,            | 2.0            | l dB                         |

|--------------|----------------|------------------------------|

|              | 0.0            | l dis                        |

| t associated | with the test  | socket and fixture           |

| 211          | ent associated | ent associated with the test |

**Fig. 5.30** MOSFET 2N3797 tipo depleção de canal *n* da Motorola.\*

chamada substrato. Como no MOSFET tipo depleção, em certas ocasiões o substrato está conectado internamente ao terminal de fonte, e em outras temos um quarto terminal disponível para o controle do potencial do substrato. Os terminais de fonte e dreno estão conectados novamente às regiões *n*-dopadas, através de contatos metálicos, mas observe na Fig. 5.31 que não há um canal entre as duas regiões *n*-dopadas. Esta é a diferença principal que existe entre a construção do MOSFET tipo depleção e a construção do MOSFET tipo intensificação — a ausência de um ca-

nal como um componente do dispositivo. A camada de  $SiO_2$  está presente para isolar a plataforma metálica da porta da região entre o dreno e a fonte, que, neste caso, é o substrato tipo p. Em resumo, portanto, a construção de um MOSFET tipo intensificação

pAde

<sup>\*</sup>N.T.: Os termos originais em inglês contidos nesta figura não foram traduzidos porque o que se encontra na prática, no laboratório, são especificações escritas em inglês, com raras exceções. Deseja-se, com isto, que o leitor se acostume aos termos técnicos que ele encontrará na sua vida profissional.

Fig. 5.31 MOSFET tipo intensificação de canal n.

é bem semelhante à do MOSFET tipo depleção, sendo a diferença principal a ausência de um canal entre os terminais de dreno e fonte no tipo intensificação.

# Operação Básica e Características

Se  $V_{GS}$  for igual a 0 V e uma tensão for aplicada entre o dreno e fonte do dispositivo, a ausência do canal n (com uma quantidade generosa de portadores livres) não permite que circule uma corrente de dreno — bem diferente do MOSFET tipo depleção e JFET, onde  $I_D = I_{DSS}$ . Não basta acumular grande número de portadores (elétrons) no dreno e fonte (devido às regiões n-dopadas), se não existir um caminho entre os dois. Com  $V_{DS}$  positiva,  $V_{GS}$  em 0 V, e o terminal SS conectado diretamente à fonte, existem, na verdade, duas junções p-n reversamente polarizadas entre as regiões n-dopadas e o substrato p que se opõe a qualquer fluxo significativo entre o dreno e a fonte.

Na Fig. 5.32, tanto  $V_{DS}$  como  $V_{GS}$  são tensões positivas, estabelecendo desta forma um potencial positivo para o dreno e porta em relação à fonte. O potencial positivo na porta irá pressionar os buracos (já que os campos se repelem) para o substrato p ao longo da camada isolante de SiO2, fazendo-os penetrar no substrato até as camadas mais profundas, como mostrado na figura. O resultado é uma região de depleção próxima à camada isolante SiO2 livre de elétrons. Entretanto, os elétrons no substrato p (os portadores minoritários do material) serão atraídos para a porta, que está com um potencial positivo, e se acumularão próximos à superfície da camada de SiO2. A camada de SiO2 isolante evitará que os portadores negativos sejam aborrecidos no terminal de porta. Na medida em que  $V_{GS}$  aumenta de valor, a concentração de elétrons próximo da superfície se intensifica até um nível em que a região induzida tipo n possa suportar o fluxo entre o dreno e a fonte. O nível de  $V_{GS}$  que produz um aumento significativo da corrente de dreno é chamado de tensão de limiar, representado pelo símbolo  $V_T$ . Nas folhas de especificações é denominado  $V_{GS(Th)}$ ; entretanto  $V_T$  é mais utilizado e será este o símbolo adotado na análise a seguir. Uma vez que não há canal com  $V_{GS} = 0$  V e "intensificado" pela aplicação de uma tensão porta-fonte positiva, este tipo de MOSFET é chamado de Elétrons atraídos para a porta com potencial positivo (canal n induzido)

Fig. 5.32 Formação do canal no MOSFET de canal n tipo intensificação.

*MOSFET tipo intensificação*. Os dois tipos de MOSFETs possuem regiões tipo intensificação, mas o nome foi dado a apenas um, porque é o seu único modo de operação.

Quando  $V_{GS}$  aumenta a partir do nível de limiar, a densidade de portadores livres no canal induzido aumentará, resultando em um aumento na corrente de dreno. Entretanto, se mantivermos  $V_{GS}$  constante e aumentarmos o valor de  $V_{DS}$ , a corrente de dreno deverá atingir um nível de saturação, como ocorreu para o JFET e para o MOSFET tipo depleção. A manutenção de  $I_D$  em um nível fixo é devida ao processo de constrição (pinch-off), que torna o canal induzido mais estreito próximo ao dreno, como mostrado na Fig. 5.33. Aplicando a lei das tensões de Kirchhoff às tensões dos terminais da Fig. 5.33, achamos que

$$V_{DG} = V_{DS} - V_{GS} (5.11)$$

Se  $V_{GS}$  for mantido em um valor fixo, como, p. ex., 8 V, e  $V_{DS}$  aumentado de 2 V para 5 V, a tensão  $V_{DG}$  [pela Eq. (5.11)] cairá de -6 V para -3 V, e a porta se tornará cada vez menos positiva com relação ao dreno. A redução da tensão porta-dreno irá por sua vez reduzir as forças atrativas para os portadores livres (elétrons) nesta região do canal induzido, causando uma redução na largura do canal. Eventualmente, o canal será reduzido até o ponto de pinch-off e uma condição de saturação será estabelecida como descrito anteriormente para o JFET e o MOSFET tipo depleção. Em outras palavras, qualquer aumento adicional em  $V_{DS}$ , mantendo-se fixa a tensão  $V_{GS}$ , não afetará o nível de saturação de  $I_D$  até que se atinjam as condições de ruptura.

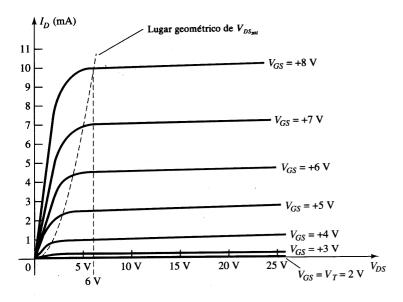

As curvas características de dreno da Fig. 5.34 revelam que para o dispositivo da Fig. 5.33 com  $V_{GS} = 8$  V, a saturação ocorre para  $V_{DS} = 6$  V. Na verdade, o nível de saturação de  $V_{DS}$  é relacionado ao valor da tensão  $V_{GS}$  aplicada por

$$V_{DS_{\text{sat}}} = V_{GS} - V_T \tag{5.12}$$

**Fig. 5.33** Alterações no canal e na região de depleção com o aumento de  $V_{DS}$  para um valor fixo de  $V_{GS}$ .

Obviamente, portanto, mantendo-se fixo  $V_T$  e aumentando-se o valor de  $V_{GS}$ , maior é o nível de saturação para  $V_{DS}$ , como mostrado na Fig. 5.33 pelo lugar geométrico dos níveis de saturação.

Na Fig. 5.34, o nível de  $V_T$  é 2 V, uma vez que não existe corrente de dreno para esta situação. Em geral, portanto:

Para valores de  $V_{\rm GS}$  menores do que o nível de limiar em um MOSFET tipo intensificação, não há corrente de dreno.

A Fig. 5.34 revela que quando o nível de  $V_{GS}$  aumenta de  $V_T$  para 8 V, o nível de  $I_D$  também se eleva, indo de 0 mA para 10 mA. Além disso, observa-se claramente que o espaçamento en-

tre as curvas aumenta quando  $V_{\rm GS}$  aumenta de valor, resultando em incrementos sempre crescentes para a corrente de dreno.

Para valores de  $V_{GS} > V_T$ , a corrente de dreno está relacionada com a tensão porta-fonte pela seguinte relação não-linear:

$$I_D = k(V_{GS} - V_T)^2 (5.13)$$

Novamente, o termo quadrático é o responsável pela relação nãolinear entre  $I_D$  e  $V_{GS}$ . O termo k é uma constante que é função da construção do dispositivo. O valor de k pode ser determinado da seguinte equação [derivada da Eq. (5.13)], onde  $I_{D(\text{on})}$  e  $V_{GS(\text{on})}$ representam um ponto particular das curvas do dispositivo.

$$k = \frac{I_{D(\text{on})}}{(V_{GS(\text{on})} - V_T)^2}$$

(5.14)

Substituindo  $I_{D(\text{on})}=10 \text{ mA}$  quando  $V_{GS(\text{on})}=8 \text{ V}$ , das curvas da Fig. 5.34, temos que

$$k = \frac{10 \text{ mA}}{(8 \text{ V} - 2 \text{ V})^2} = \frac{10 \text{ mA}}{(6 \text{ V})^2} = \frac{10 \text{ mA}}{36 \text{ V}^2}$$

$$= \mathbf{0.278 \times 10^{-3} \text{ A/V}^2}$$

e encontrando a equação geral para  $I_D$ :

$$I_D = 0.278 \times 10^{-3} (V_{GS} - 2 \text{ V})^2$$

Substituindo  $V_{GS} = 4 \text{ V}$ , achamos que

$$I_D = 0.278 \times 10^{-3} (4 \text{ V} - 2 \text{ V})^2 = 0.278 \times 10^{-3} (2)^2$$

= 0.278 × 10<sup>-3</sup>(4) = **1.11 mA**

como pode ser verificado na Fig. 5.34. Em  $V_{GS} = V_T$  o termo quadrático se anula, e  $I_D = 0$  mA.

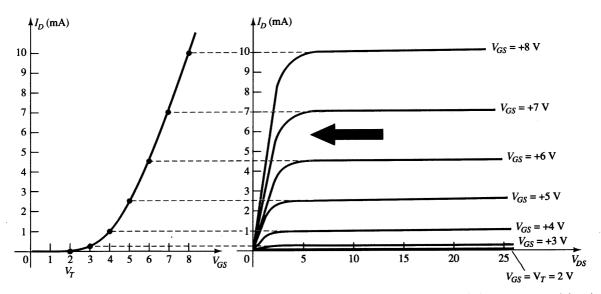

Para a análise de do MOSFET tipo intensificação a ser realizada no Cap. 6, as curvas características de transferência serão novamente as curvas empregadas para uma solução gráfica. Na Fig. 5.35, as curvas de dreno e de transferência foram colocadas lado a lado para descreverem o procedimento de transferência de uma para a outra. Este processo é realizado, essencialmente, da mesma forma descrita anteriormente para o JFET e o MOSFET

**Fig. 5.34** Características de dreno de um MOSFET tipo intensificação de canal  $n \text{ com } V_T = 2 \text{ V e } k = 0.278 \times 10^{-3} \text{ A/V}^2$ .

Fig. 5.35 Esboçando a curva característica de transferência para um MOSFET tipo intensificação de canal n, a partir das curvas características de dreno.

tipo depleção. Neste caso, entretanto, deve ser lembrado que a corrente de dreno é 0 mA para  $V_{GS} \leq V_T$ . Acima deste nível, surge uma corrente  $I_D$  cujo valor é determinado pela Eq. (5.13). Observe que na definição dos pontos da curva de transferência a partir da curva de dreno, somente os níveis de saturação são empregados, e por isso a região de operação é limitada aos valores de  $V_{DS}$  maiores do que os níveis de saturação, como definido pela Eq. (5.12).

A curva de transferência da Fig. 5.35 é certamente bem diversa daquela obtida anteriormente. Para um dispositivo de canal n (induzido), a curva está agora completamente na região de valores positivos de  $V_{GS}$  e decresce a partir de  $V_{GS} = V_T$ . A questão que surge agora é como traçar as curvas de transferência dados os valores de k e  $V_T$ , como feito a seguir para um MOSFET específico:

$$I_D = 0.5 \times 10^{-3} (V_{GS} - 4 \text{ V})^2$$

Inicialmente, uma linha horizontal é desenhada em  $I_D = 0$  mA, de  $V_{GS} = 0$  V até  $V_{GS} = 4$  V como mostrado na Fig. 5.36a. Após isso, um valor para  $V_{GS}$  maior do que  $V_T$  (como, p. ex., 5 V) é escolhido e substituído na Eq. (5.13), para determinar o nível resultante de  $I_D$ :

$$I_D = 0.5 \times 10^{-3} (V_{GS} - 4 \text{ V})^2$$

= 0.5 × 10<sup>-3</sup>(5 V - 4 V)<sup>2</sup> = 0.5 × 10<sup>-3</sup>(1)<sup>2</sup>

= **0.5 mA**

e um ponto no gráfico é obtido como mostra a Fig. 5.36b. Para completar o traçado, outros valores para  $V_{GS}$  são escolhidos, e os níveis correspondentes de  $I_D$  obtidos. Em particular, em  $V_{GS}=6$  V, 7 V e 8 V, o nível de  $I_D$  é 2 mA, 4,5 mA e 8 mA, respectivamente, como mostrado no gráfico resultante da Fig. 5.36c.

# MOSFETs Tipo Intensificação de Canal p

A construção de um MOSFET tipo intensificação de canal p é exatamente o inverso do que aparece na Fig. 5.31. Ou seja, o substrato agora é o tipo n, e as regiões abaixo das conexões de

dreno e fonte são p-dopadas. Os terminais são identificados da mesma forma, mas todas as polaridades das tensões e os sentidos das correntes são invertidos. As curvas características de dreno terão o aspecto mostrado na Fig. 5.37c, mostrando que quanto mais negativo  $V_{GS}$ , maior é a corrente de dreno. A curva de transferência apresenta o mesmo formato da curva da Fig. 5.35, porém refletida em relação ao eixo  $I_D$ , com  $I_D$  crescente para valores de  $V_{GS}$  negativos decrescentes (crescentes em módulo) abaixo de  $V_T$ , como mostra a Fig. 5.37b. As Equações (5.11) até a (5.14) são igualmente aplicáveis aos dispositivos de canal p.

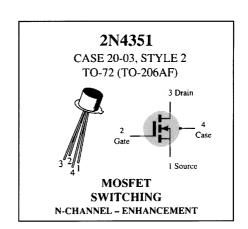

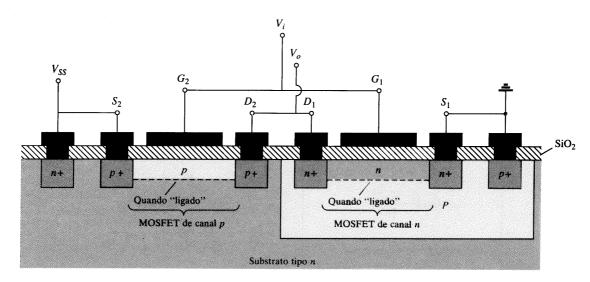

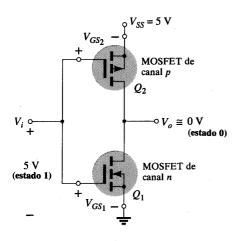

# Símbolos, Folhas de Especificações e Encapsulamento

Os símbolos gráficos para os MOSFETs tipo intensificação de canal n e p são apresentados na Fig. 5.38. Observe novamente que os símbolos tentam refletir a construção real do dispositivo. A linha pontilhada entre o dreno e a fonte significa que não há um canal entre os dois terminais sob condições de não-polarização. É, na verdade, a única diferença entre os símbolos dos MOSFETs tipo depleção e tipo intensificação.

A folha de especificações para o MOSFET tipo intensificação de canal n da Motorola é mostrada na Fig. 5.39. O tipo de encapsulamento e a identificação dos terminais são fornecidos próximos às especificações máximas do dispositivo, que agora inclui uma corrente máxima de dreno de 30 mA dc. A folha de especificações fornece o nível de  $I_{DSS}$  sob condições de "não condução", que para este caso é apenas 10 nA dc (em  $V_{DS}=10$  V,  $V_{GS}=0$  V), bem menor do que o verificado para o JFET e o MOSFET tipo depleção. A tensão de limiar é denominada de  $V_{GS(Th)}$ , e varia de 1 até 5 V dc, dependendo do dispositivo empregado. A folha de especificações não fornece o valor de k da Eq. (5.13), entretanto especifica um valor típico de  $I_{D(on)}$  (3 mA neste caso) para um nível de  $V_{GS(on)}$  (10 V para este valor de  $I_D$ ). Em outras palavras, quando  $V_{GS}=10$  V,  $I_D=3$  mA. Os valores apresentados de  $V_{GS(Th)}$ ,  $I_{D(on)}$  e  $V_{GS(on)}$  permitem uma determinação de k baseada na Eq. (5.14) e, deste modo, obtemos a equação geral para a curva de transferência. As características do

**Fig. 5.36** Traçando a curva de transferência de um MOSFET tipo intensificação com  $k=0.5\times10^{-3}~{\rm A/V^2}~{\rm e}~V_T=4~{\rm V}.$

Fig. 5.37 MOSFET tipo intensificação de canal p com  $V_T=2$  V e  $k=0.5\times 10^{-3}$  A/V<sup>2</sup>.

**Fig. 5.38** Símbolos para (a) MOSFET tipo intensificação de canal n e (b) MOSFET tipo intensificação de canal p.

MOSFET que devem ser observadas quando do emprego do dispositivo são revistas na Seção 5.9.

# **EXEMPLO 5.4**

Utilizando os dados fornecidos na folha de especificações da Fig. 5.39 e considerando uma tensão limiar de  $V_{GS(Th)} = 3 \text{ V}$ , determine:

- (a) O valor resultante de k para o MOSFET.

- (b) A curva de transferência

# Solução

(a) Eq. (5.14):

$$k = \frac{I_{D(\text{on})}}{(V_{GS(\text{on})} - V_{GS(\text{Th})})^2}$$

$$= \frac{3 \text{ mA}}{(10 \text{ V} - 3 \text{ V})^2} = \frac{3 \text{ mA}}{(7 \text{ V})^2} =$$

$$= \frac{3 \times 10^{-3}}{49} \text{ A/V}^2$$

$$= \mathbf{0.061} \times \mathbf{10^{-3}} \text{ A/V}^2$$

(b) Eq. (5.13):

$$I_D = k(V_{GS} - V_T)^2$$

$$= 0.061 \times 10^{-3}(V_{GS} - 3 \text{ V})^2$$

Para

$$V_{GS} = 5 \text{ V}$$

$$I_D = 0.061 \times 10^{-3}(5 \text{ V} - 3 \text{ V})^2 =$$

$$= 0.061 \times 10^{-3}(2)^2$$

$$= 0.061 \times 10^{-3}(4) = 0.244 \text{ mA}$$

Para  $V_{GS} = 8$  V, 10 V e 12 V,  $I_D$  será 1,525 mA, 3 mA (como previsto) e 4,94 mA, respectivamente. A curva de transferência é esboçada na Fig. 5.40.

# 5.9 EMPREGO DO MOSFET

A camada de SiO<sub>2</sub> entre a porta e o canal do MOSFET proporciona a agradável característica de alta impedância de entrada para

o dispositivo; entretanto, a largura extremamente reduzida da camada introduz um problema para o emprego do MOSFET, e que não existia para o TBJ e JFET. Normalmente, há um acúmulo suficiente de carga estática (devido a condições externas) que estabelece uma diferença de potencial através da fina camada e que pode, eventualmente, danificá-la e permitir a condução através desta. É, portanto, imperativo que se utilize algum mecanismo para manter os terminais do dispositivo conectados até que o mesmo seja inserido no sistema. Desta maneira, evita-se a possibilidade do surgimento de um potencial entre dois terminais do dispositivo. Com a conexão, a diferença de potencial entre quaisquer dois terminais é mantida em 0 V. Por último, toque sempre os terminais no terra para permitir a descarga das cargas estáticas acumuladas, antes de empregar o dispositivo, e sempre o manuseie segurando pelo encapsulamento.

Via de regra, ocorrem transientes (mudanças abruptas no nível de tensão ou corrente) em um circuito, quando elementos são removidos ou inseridos com a fonte ligada. Às vezes, os níveis de transiente podem ultrapassar os limites que o dispositivo suporta, e por esta razão, a fonte deve estar sempre desligada ao modificarmos a configuração do circuito.

A máxima tensão porta-fonte normalmente é fornecida na folha de especificações do dispositivo. Um método para assegurar que esta tensão não será ultrapassada (talvez devido a transientes) em ambas as polaridades é introduzir dois diodos Zener, como mostra a Fig. 5.41. Os Zeners são colocados em posições opostas um do outro. Se são utilizados Zeners de 30 V e surge no circuito um transiente positivo de 40 V, o Zener mais abaixo na figura irá "disparar" em 30 V, e o diodo acima irá ligar com uma queda de tensão de zero volt (idealmente — para a região positiva "ligada" de um diodo semicondutor). O resultado é que limitamos a tensão porta-fonte em 30 V. Uma desvantagem introduzida pelo Zener é que a resistência de um diodo Zener "desligado" é menor do que a impedância de entrada estabelecida pela camada SiO2. A impedância de entrada é reduzida, mas mesmo assim é grande o suficiente para a maioria das aplicações. Tantos são os dispositivos discretos que possuem a proteção por Zener, que alguns dos problemas listados acima não incomodam mais. Entretanto, devemos ser ainda bem cautelosos quando do emprego de dispositivos MOSFET discretos.

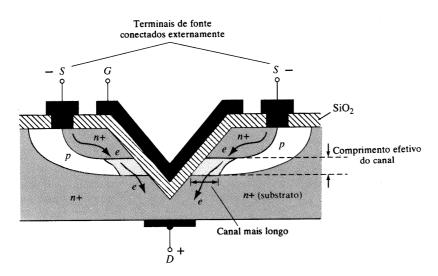

# 5.10 VMOS

Uma das desvantagens do MOSFET, quando comparado ao TBJ, é o seu nível reduzido de potência de operação (tipicamente, menor do que 1 W). Esta deficiência para um dispositivo com tantas características positivas pode ser minimizada modificando-se o modo de construção, onde se abandona a estrutura planar, como consta na Fig. 5.23, e adota-se uma estrutura vertical do tipo mostrado na Fig. 5.42. Todos os elementos do MOSFET planar estão presentes no FET metal-óxido-semicondutor vertical (VMOS) — a superfície metálica de contato para os terminais do dispositivo — a camada de SiO2 entre a porta e a região tipo p localizada entre o dreno e a fonte, para o crescimento do canal n induzido (operação tipo intensificação). O termo vertical é devido principalmente ao fato de o canal ser agora formado na direção vertical, ao contrário do que ocorria para o dispositivo planar, onde o crescimento era horizontal. O canal da Fig. 5.42 também possui o aspecto de um corte em V na base semicondutora que, para alguns, pode servir como uma característica para a memorização do nome do dispositivo. A construção mostrada

#### MAXIMUM RATINGS

| Rating                                                             | Symbol           | Value       | Unit       |  |

|--------------------------------------------------------------------|------------------|-------------|------------|--|

| Drain-Source Voltage                                               | V <sub>DS</sub>  | 25          | Vdc        |  |

| Drain-Gate Voltage                                                 | $V_{DG}$         | 30          | Vdc        |  |

| Gate-Source Voltage*                                               | $V_{GS}$         | 30          | Vdc        |  |

| Drain Current                                                      | I <sub>D</sub>   | 30          | mAdc       |  |

| Total Device Dissipation @ T <sub>A</sub> = 25°C Derate above 25°C | P <sub>D</sub>   | 300<br>1.7  | mW<br>mW/C |  |

| Junction Temperature Range                                         | T <sub>J</sub>   | 175         | °C         |  |