# Configurações 12 Compostas

## 12.1 INTRODUÇÃO

Neste capítulo, introduzimos uma variedade de conexões de circuitos, que, embora sejam configurações emissor-comum, coletor-comum, ou base-comum fora do padrão habitual, ainda são bastante importantes, sendo amplamente usadas quer sejam em circuitos discretos ou integrados. A conexão em cascata é constituída de estágios em série, enquanto a conexão cascode coloca um transistor no topo de outro. Estas formas de conexão são encontradas em circuitos na prática. A conexão Darlington e a conexão par realimentado representam múltiplos transistores conectados operando como se fossem um simples transistor com a finalidade de melhorar o seu desempenho, usualmente com um ganho de corrente muito maior.

A conexão CMOS, usando transistores MOSFET intensificação tipo *p* e tipo *n* num circuito operando com potência muito baixa, é introduzida neste capítulo. Muitos dos circuitos digitais mais recentes usam circuitos CMOS, quer seja para permitir sua operação, em termos de portabilidade, com uma potência de bateria muito baixa, quer seja para permitir uma densidade de integração muito alta em circuitos integrados, com uma dissipação de potência muito baixa num pequeno espaço ocupado pelo chip do CI.

Ambos os circuitos discretos e integrados usam a conexão fonte de corrente. A conexão espelho de corrente fornece corrente constante para vários outros circuitos e é especialmente importante em circuitos lineares integrados.

O amplificador diferencial é a parte básica de circuitos amplificadores operacionais (cobertos completamente no Cap. 14). A conexão básica de um circuito diferencial e sua operação são introduzidas neste capítulo. Embora colocada no fim do capítulo, é, apesar disso, a conexão de circuito mais importante. Um circuito bipolar-JFET usado em CIs é a conexão BiFET, enquanto a conexão bipolar-MOSFET é chamada conexão BiMOS. Essas configurações são usadas em circuitos lineares integrados.

## 12.2 CONEXÃO EM CASCATA

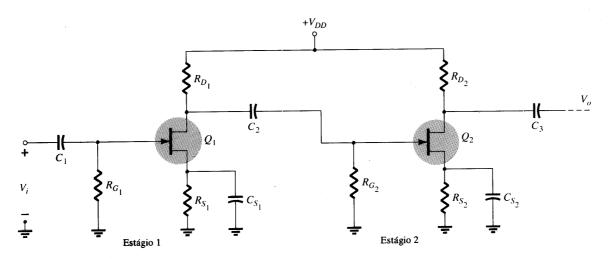

Uma conexão popular de estágios amplificadores é a conexão em cascata. Basicamente, a conexão em cascata é uma série de acoplamentos de estágios em que a saída de um estágio repre-

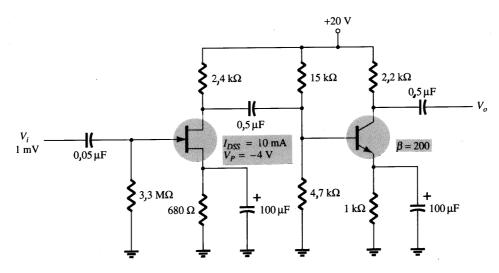

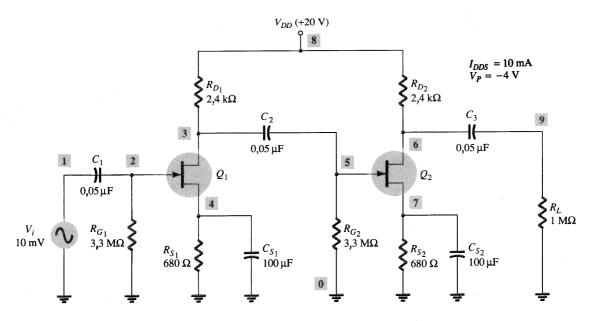

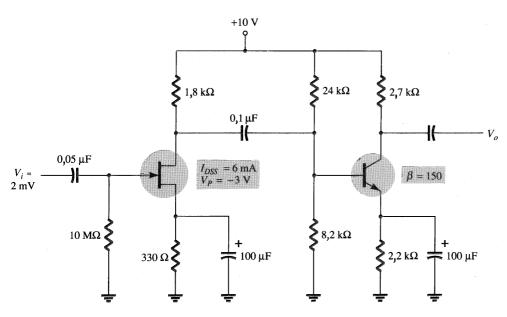

senta o sinal de entrada do estágio seguinte. A Fig. 12.1 mostra uma conexão em cascata de dois estágios amplificadores a FET. A conexão em cascata proporciona uma multiplicação do ganho de cada estágio, resultando num ganho global muito maior.

O ganho global do amplificador em cascata é o produto dos ganhos  $A_{\nu_1}$  e  $A_{\nu_2}$  dos estágios,

$$A_{v} = A_{v_0} A_{v_0} = (-g_{m_0} R_{D_0}) (-g_{m_0} R_{D_0})$$

(12.1)

A impedância de entrada do amplificador em cascata é aquela do estágio 1,

$$Z_i = R_{G_i} \tag{12.2}$$

enquanto a impedância de saída é aquela do estágio 2.

$$Z_o = R_{D_0} \tag{12.3}$$

A função principal dos estágios em cascata é conseguir um ganho global muito maior. Como a polarização de e os cálculos ac para um amplificador em cascata utilizam as equações deduzidas para os estágios individuais, no próximo exemplo aplicam-se estas equações para a análise de um amplificador em cascata.

## EXEMPLO 12.1

Calcule a polarização dc, ganho de tensão, impedância de entrada, impedância de saída, e a tensão de saída resultante para o amplificador em cascata mostrado na Fig. 12.2. Calcule a tensão na carga, se uma carga de 10-k $\Omega$  for conectada na saída.

## Solução

Ambos os estágios amplificadores têm a mesma polarização dc. Usando as técnicas de polarização dc do Cap. 6, resulta em

$$V_{GS_Q} = -1.9 \text{ V}, I_{D_Q} = 2.8 \text{ mA}$$

Ambos os transistores têm

$$g_{m0} = \frac{2I_{DSS}}{|V_P|} = \frac{2(10 \text{ mA})}{|-4 \text{ V}|} = 5 \text{ mS}$$

Fig. 12.1 Amplificador a FET em cascata.

e no ponto de polarização dc,

$$g_m = g_{m0} \left( 1 - \frac{V_{GS_Q}}{V_P} \right) = (5 \text{ mS}) \left( 1 - \frac{-1.9 \text{ V}}{-4 \text{ V}} \right) = 2.6 \text{ mS}$$

O ganho de tensão de cada estágio é então

$$A_{v_1} = A_{v_2} = -g_m R_D = -(2.6 \text{ mS})(2.4 \text{ k}\Omega) = -6.2$$

O ganho de tensão do amplificador em cascata é, então,

Eq. (12.1):

$$A_v = A_{v_1} A_{v_2} = (-6.2)(-6.2) = 38.4$$

A tensão de saída é, então,

$$V_o = A_v V_i = (38.4) (10 \text{ mV}) = 384 \text{ mV}$$

A impedância de entrada do amplificador em cascata é

$$Z_i = R_G = 3.3 \,\mathrm{M}\Omega$$

A impedância de saída do amplificador em cascata (assumindo que  $r_d = \infty$ ) é

$$Z_o = R_D = 2.4 \text{ k}\Omega$$

A tensão de saída através da carga de 10-k $\Omega$  seria então

$$V_L = \frac{R_L}{Z_o + R_L} V_o = \frac{10 \text{ k}\Omega}{2.4 \text{ k}\Omega + 10 \text{ k}\Omega} (384 \text{ mV}) = 310 \text{ mV}$$

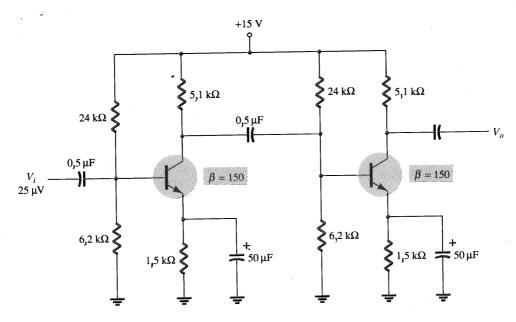

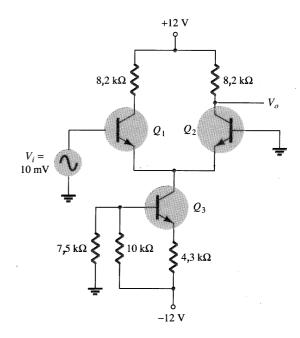

## Amplificador TBJ em Cascata

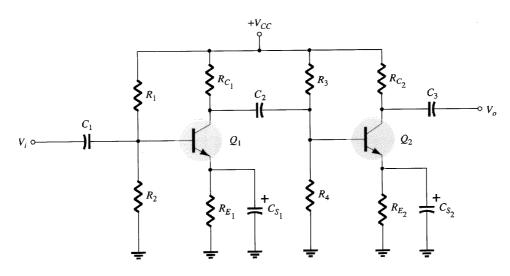

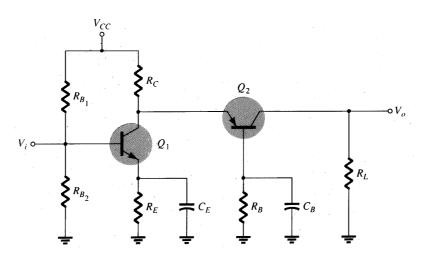

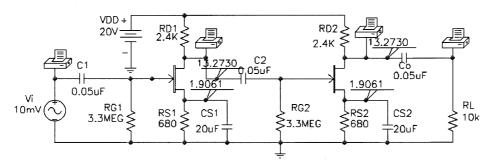

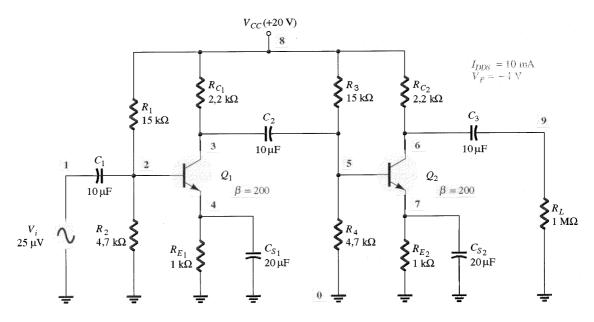

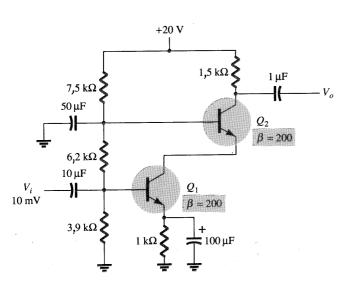

Um amplificador em cascata com acoplamento *RC* construído usando TBJs é mostrado na Fig. 12.3. Como antes, a vantagem de estágios em cascata é o ganho global de tensão. A polarização de é obtida usando os procedimentos do Cap. 4. O ganho de tensão de estágio é

$$A_{v} = \frac{-R_{C}||R_{L}|}{r_{e}} \tag{12.4}$$

A impedância de entrada do amplificador é aquela do estágio 1,

$$Z_{i} = R_{1} \parallel R_{2} \parallel \beta r_{e} \tag{12.5}$$

Fig. 12.2 Circuito amplificador em cascata para o Exemplo 12.1.

Fig. 12.3 Amplificador TBJ em cascata (acoplamento RC).

e a impedância de saída do amplificador é aquela do estágio 2,

$$Z_o = R_C \parallel r_o \tag{12.6}$$

O próximo exemplo demonstra a análise de um amplificador TBJ em cascata, mostrando o grande ganho de tensão conseguido.

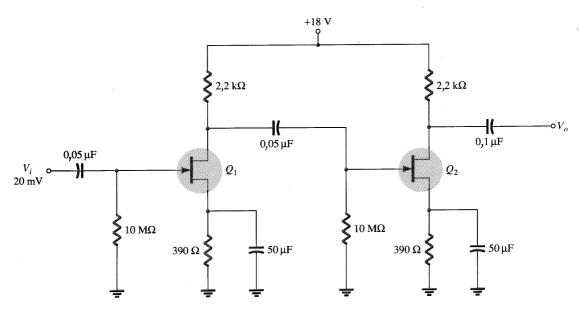

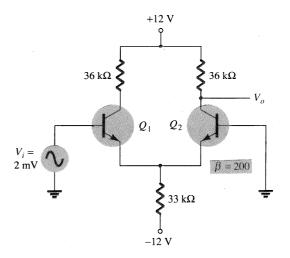

## EXEMPLO 12.2

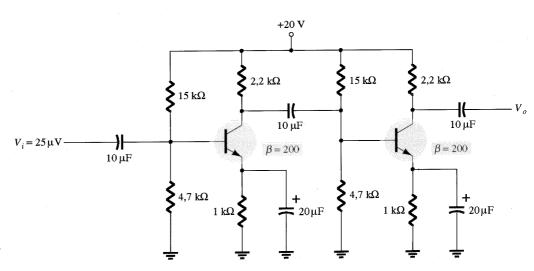

Calcule o ganho de tensão, impedância de entrada e a impedância de saída para o amplificador TBJ em cascata da Fig. 12.4. Calcule a tensão de saída resultante se uma carga de 10-k $\Omega$  for conectada na saída.

## Solução

A análise de polarização de resulta em

$$V_R = 4.7 \text{ V}, \qquad V_E = 4.0 \text{ V}, \quad V_C = 11 \text{ V}, I_E = 4.0 \text{ mA}$$

No ponto de polarização,

$$r_e = \frac{26}{I_E} = \frac{26}{4,0} = 6.5 \ \Omega$$

O ganho de tensão do estágio 1 é então

$$A_{\nu_1} = -\frac{R_C ||(R_1 || R_2 || \beta r_e)}{r_e}$$

$$= -\frac{(2.2 \text{ k}\Omega) ||[15 \text{ k}\Omega || 4.7 \text{ k}\Omega || (200)(6.5 \Omega)]}{6.5 \Omega}$$

$$= -\frac{665.2 \Omega}{6.5 \Omega} = -102.3$$

enquanto o ganho de tensão do estágio 2 é

$$A_{v_2} = -\frac{R_C}{r_e} = -\frac{2.2 \text{ k}\Omega}{6.5 \Omega} = -338,46$$

para um ganho de tensão global de

$$A_{\nu} = A_{\nu,A_{\nu_2}} = (-102,3)(-338,46) =$$

**34.624**

**Fig. 12.4** Amplificador TBJ com acoplamento *RC* para o Exemplo 12.2.

Fig. 12.5 Amplificador JFET-TBJ em cascata para o Exemplo 12.3.

A tensão de saída é então

$$V_o = A_v V_i = (34.624)(25 \ \mu V) = 0.866 \ V$$

A impedância de entrada do amplificador é

$$Z_i = R_1 ||R_2|| βr_e = 4.7 \text{ k}Ω||15 \text{ k}Ω||(200)(6.5 \Omega)$$

= **953.6 Ω**

enquanto a impedância de saída do amplificador é

$$Z_o = R_C = 2.2 \text{ k}\Omega$$

Se uma carga de 10-k $\Omega$  for conectada na saída do amplificador, a tensão resultante na carga é

$$V_L = \frac{R_L}{Z_o + R_L} V_o = \frac{10 \text{ k}\Omega}{2.2 \text{ k}\Omega + 10 \text{ k}\Omega} (0.866 \text{ V}) = 0.71 \text{ V}$$

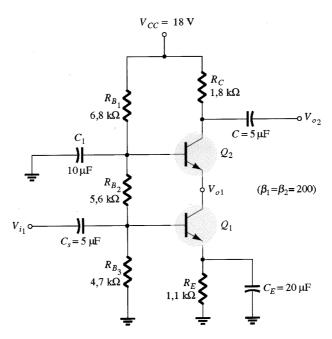

Uma combinação de estágios a FET e TBJ pode também ser usada para obter alto ganho de tensão e alta impedância de entrada, como demonstrado pelo próximo exemplo.

### EXEMPLO 12.3

Para o amplificador em cascata da Fig. 12.5, calcule a polarização de em seguida a impedância de entrada, impedância de saída, ganho de tensão e a tensão de saída resultante.

### Solução

Uma vez que  $R_i$  (estágio 2) = 15 k $\Omega$  || 4,7 k $\Omega$  || 200 (6,4  $\Omega$ ) = 943  $\Omega$ , o ganho do estágio 1 (quando carregado pelo estágio 2) é

$$A_{v_1} = -g_m[R_D||R_i \text{ (estágio 2)}]$$

= -2.6 mS(2,4 k\O||953,6 \Omega) = -1.77

do Exemplo 12.2, o ganho de tensão do estágio 2 é  $A_{\nu_2}=-349$ . O ganho de tensão global é, então,

$$A_{\nu} = A_{\nu}A_{\nu} = (-1,77)(-338,46) = 599,1$$

A tensão de saída é, então,

$$V_o = A_v V_1 = (599.1)(1 \text{ mV}) \approx 0.6 \text{ V}$$

A impedância de entrada do amplificador é aquela do estágio 1,

$$Z_i = 3.3 \text{ M}\Omega$$

enquanto a impedância de saída é aquela do estágio 2,

$$Z_o = R_D = 2.2 \text{ k}\Omega$$

## 12.3 CONEXÃO CASCODE

Uma conexão cascode tem um transistor acima (em série com) de um outro. A Fig. 12.6 mostra uma configuração cascode com um estágio emissor-comum (EC) alimentando um estágio base-comum (BC). Este arranjo é projetado para prover uma alta impedância de entrada com baixo ganho de tensão, assegurando que a capacitância Miller de entrada (veja Cap. 11) seja mínima, com o estágio BC proporcionando uma boa operação em alta freqüência. Uma versão utilizada na prática de um amplificador cascode com TBJ é fornecida na Fig. 12.7.

### EXEMPLO 12.4

Calcule o ganho de tensão para o amplificador cascode da Fig. 12.7.

## Solução

A análise da polarização de usando os procedimentos do Cap. 4 resulta em

$$V_{B_1} = 4.9 \text{ V}, \qquad V_{B_2} = 10.8 \text{ V}, \qquad I_{C_1} \approx I_{C_2} = 3.8 \text{ mA}$$

A resistência dinâmica de cada transistor é, então,

$$r_e = \frac{26}{I_E} = \frac{26}{3.8} = 6.8 \ \Omega$$

Fig. 12.6 Configuração cascode

O ganho de tensão do estágio 1 (emissor-comum) é aproximadamente

$$A_{\nu_1} = -\frac{R_C}{r_e} = -\frac{r_e}{r_e} = -1$$

O ganho de tensão do estágio 2 (base-comum) é

$$A_{\nu_2} = \frac{R_C}{r_e} = \frac{1.8 \text{ k}\Omega}{6.8 \Omega} = 265$$

resultando num ganho global do amplificador cascode de

$$A_{\nu} = A_{\nu_1} A_{\nu_2} = (-1)(265) = -265$$

Como esperado, o estágio CE com um ganho de -1 proporciona a impedância de entrada mais alta de um estágio CE (superior à do estágio BC). Com um ganho de tensão de apenas -1,

a capacitância Miller de entrada é mantida muito pequena. Um alto ganho de tensão é então proporcionado pelo estágio BC, resultando num grande ganho global ( $A_{\nu} = -265$ ).

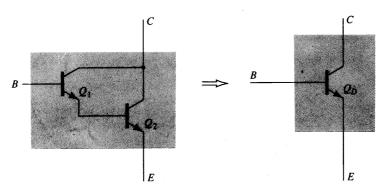

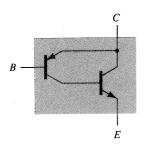

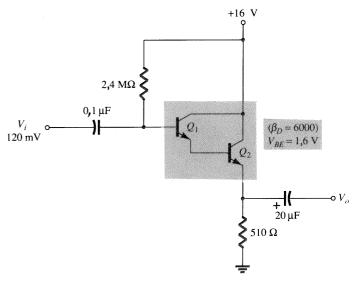

## 12.4 CONEXÃO DARLINGTON

Uma conexão muito popular de dois transistores bipolares de junção operando como um transistor "superbeta" é a conexão Darlington mostrada na Fig. 12.8. A característica principal da conexão Darlington é que a composição de transistores atua como uma unidade única, com um ganho de corrente que é o produto dos ganhos de corrente dos transistores individuais. Se a conexão for feita usando dois transistores separados com ganhos de corrente  $\beta_1$  e  $\beta_2$ , a conexão Darlington fornece um ganho de corrente de

$$\beta_D = \beta_1 \beta_2 \tag{12.7}$$

Fig. 12.7 Circuito cascode para o Exemplo 12.4.

Fig. 12.8 Constituição de um transistor Darlington.

Se os dois transistores estão casados de tal forma que  $\beta_1 = \beta_2 = \beta$ , a conexão Darlington fornece um ganho de corrente de

$$\beta_D = \beta^2 \tag{12.8}$$

Uma conexão de transistor Darlington equivale a um transistor com um ganho de corrente muito alto, tipicamente na faixa de alguns milhares.

## EXEMPLO 12.5

Qual o ganho de corrente fornecido por uma conexão Darlington de dois transistores idênticos, cada um com um ganho de corrente  $\beta = 200$ ?

## Solução

Eq. (12.8):

$$\beta_D = \beta^2 = (200)^2 = 40.000$$

## Transistor Darlington Encapsulado

Como a conexão Darlington é muito utilizada, pode-se construir uma pastilha contendo dois TBJs internamente conectados como um transistor Darlington. A Fig. 12.9 fornece algumas especificações de data sheets para um par Darlington típico. O ganho de corrente listado corresponde ao ganho global da conexão transistor Darlington, e o dispositivo apresenta apenas três terminais externos (base, emissor e coletor). Pode-se considerar a unidade como um simples transistor Darlington com um ganho de corrente muito alto, quando comparado a outros transistores simples típicos.

Tipo 2N999 Transistor Darlington N-P-N de Silicone em Pastilha

| Parâmetro                         | Condições de Teste                           | Mín.         | Мах.   |

|-----------------------------------|----------------------------------------------|--------------|--------|

| $V_{_{BE}}$                       | $I_C = 100 \text{ mA}$                       |              | 1,8 V  |

| $h_{FE} \ (oldsymbol{eta}_{\!D})$ | $I_C = 10 \text{ mA}$ $I_C = 100 \text{ mA}$ | 4000<br>7000 | 70.000 |

Fig. 12.9 Especificações de um transistor Darlington em pastilha (2N999).

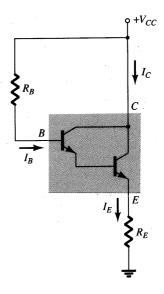

Fig. 12.10 Circuito de polarização de um Darlington básico.

## Polarização DC de um Circuito Darlington

Um circuito Darlington básico é mostrado na Fig. 12.10. Um transistor Darlington com ganho de corrente muito alto,  $\beta_D$ , é usado. A corrente de base pode ser calculada de

$$I_{B} = \frac{V_{CC} - V_{BE}}{R_{B} + \beta_{D} R_{E}} \tag{12.9}$$

Apesar de a equação acima ser a mesma de um transistor regular, o valor de  $\beta_D$  é muito grande, e o valor de  $V_{BE}$  é muito alto, conforme indicado pelos dados no quadro da Fig. 12.9. A corrente de emissor é então

$$I_E = (\beta_D + 1)I_B \approx \beta_D I_B \tag{12.10}$$

As tensões dc são

$$V_E = I_E R_E \tag{12.11}$$

$$V_B = V_E + V_{BE} (12.12)$$

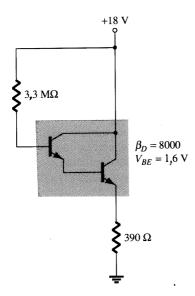

#### EXEMPLO 12.6

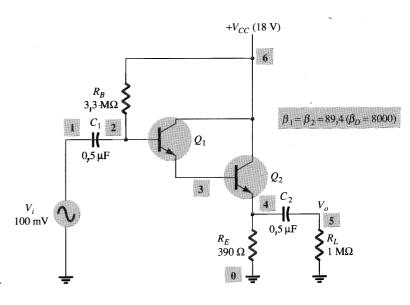

Calcule as tensões e correntes de polarização de no circuito da Fig. 12.11.

Fig. 12.11 Circuito para o Exemplo 12.6.

### Solução

A corrente de base é

Eq. (12.9):

$$I_B = \frac{18 \text{ V} - 1.6 \text{ V}}{3.3 \text{ M}\Omega + 8000(390 \Omega)} \approx 2.56 \mu\text{A}$$

A corrente de emissor é, então,

Eq. (12.10):

$$I_E \approx 8000(2,56 \ \mu\text{A}) = 20,48 \ \text{mA} \approx I_C$$

A tensão de de emissor é

Eq. (12.11):

$$V_E = 20,48 \text{ mA}(390 \Omega) \approx 8 \text{ V}$$

e a tensão de base é

Eq. (12.12):

$$V_B = 8 \text{ V} + 1.6 \text{ V} = 9.6 \text{ V}$$

Fig. 12.12 Circuito Darlington seguidor-de-emissor.

Fig. 12.13 Circuito equivalente ac de um Darlington seguidor-de-emissor.

A tensão de coletor é o valor da fonte de

$$V_C = 18 \text{ V}$$

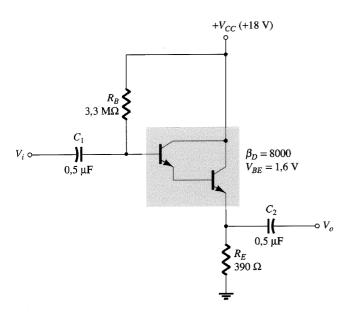

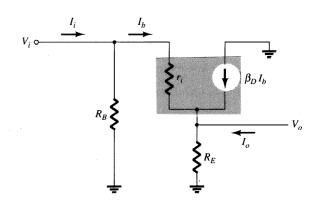

## Circuito Equivalente AC

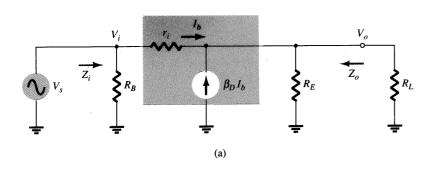

Um circuito Darlington seguidor-de-emissor é mostrado na Fig. 12.12. O sinal ac de entrada é aplicado na base do transistor Darlington através do capacitor  $C_1$ , com a saída ac,  $V_0$ , obtida do emissor através do capacitor  $C_2$ . Um circuito ac equivalente é desenhado na Fig. 12.13. O transistor Darlington é substituído por um circuito ac equivalente abrangendo uma resistência de entrada,  $r_i$ , e uma fonte de corrente na saída,  $\beta_D I_b$ .

#### IMPEDÂNCIA DE ENTRADA AC

A corrente de base ac através de  $r_i$  é

$$I_b = \frac{V_i - V_o}{r_i} \tag{12.13}$$

Uma vez que

$$V_o = (I_b + \beta_D I_b) R_E \tag{12.14}$$

Nós podemos usar a Eq. (12.13) na Eq. (12.14), para obter

$$I_b r_i = V_i - V_o = V_i - I_b (1 + \beta_D) R_E$$

Resolvendo para  $V_i$ ,

$$V_i = I_b[r_i + (1 + \beta_D)R_E] \approx I_b(r_i + \beta_D R_E)$$

A impedância de entrada ac, olhando-se para dentro da base do transistor, é então

$$\frac{V_i}{I_b} = r_i + \beta_D R_E$$

e olhando-se para dentro do circuito é

$$Z_{i} = R_{B} || (r_{i} + \beta_{D} R_{E})$$

(12.15)

## EXEMPLO 12.7

Calcule a impedância de entrada do circuito da Fig. 12.12 se  $r_i = 5 \text{ k}\Omega$ .

## ď

## Solução

Eq. (12.15).

$$Z_i = 3.3 \,\mathrm{M}\Omega \,\mathrm{II} \,[5 \,\mathrm{k}\Omega + (8000)(390 \,\Omega)] = 1.6 \,\mathrm{M}\Omega$$

#### GANHO DE CORRENTE AC

A corrente de saída ac através de  $R_E$  é (veja Fig. 12.13)

$$I_o = I_b + \beta_D I_b = (\beta_D + 1) I_b \approx \beta_D I_b$$

O ganho de corrente do transistor é então

$$\frac{I_o}{I_b} = \beta_D$$

O ganho de corrente ac do circuito é

$$A_i = \frac{I_o}{I_i} = \frac{I_o}{I_b} \frac{I_b}{I_i}$$

Podemos usar a regra do divisor de corrente para expressar  $I_b/I_i$ :

$$I_b = \frac{R_B}{(r_i + \beta_D R_E) + R_B} I_i \approx \frac{R_B}{R_B + \beta_D R_E} I_i$$

tal que o ganho de corrente ac do circuito é

$$A_i = \beta_D \frac{R_B}{R_B + \beta_D R_E} = \frac{\beta_D R_B}{R_B + \beta_D R_E}$$

(12.16)

#### EXEMPLO 12.8

Calcule o ganho de corrente ac do circuito na Fig. 12.12.

#### Solução

Eq. (12.16):

$$A_i = \frac{\beta_D R_B}{R_B + \beta_D R_E} = \frac{(8000)(3,3 \text{ M}\Omega)}{3,3 \text{ M}\Omega + (8000)(390 \Omega)} = 4112$$

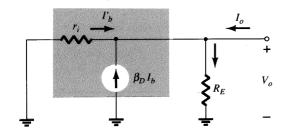

### IMPEDÂNCIA DE SAÍDA AC

A impedância de saída ac pode ser determinada pelo circuito ac mostrado na Fig. 12.14a. A impedância de saída vista pela carga  $R_L$  é determinada aplicando-se uma tensão  $V_o$ , e medindose a corrente  $I_o$  (com a entrada  $V_s$  fixada em zero). A Fig. 12.14b mostra esta situação. Resolvendo para  $I_o$ , temos

$$\begin{split} I_o &= \frac{V_o}{R_E} + \frac{V_o}{r_i} - \beta_D I_b = \frac{V_o}{R_E} + \frac{V_o}{r_i} - \beta_D \left(\frac{V_o}{r_i}\right) \\ &= \left(\frac{1}{R_E} + \frac{1}{r_i} + \frac{\beta_D}{r_i}\right) V_o \end{split}$$

Resolvendo para  $Z_o$ , obtemos

$$Z_o = \frac{V_o}{I_o} = \frac{1}{1/R_E + 1/r_i + \beta_D/r_i}$$

$$= R_E ||r_i|| \frac{r_i}{\beta_D} \approx \frac{r_i}{\beta_D}$$

(12.17)

## EXEMPLO 12.9

Calcule a impedância de saída do circuito da Fig. 12.12.

### Solução

Eq. (12.17):

$$Z_o = 390 \ \Omega || 5 \ k\Omega || \frac{5 \ k\Omega}{8000} \approx \frac{5 \ k\Omega}{8000}$$

= **0,625**  $\Omega$

(b)

Fig. 12.14 Circuito ac equivalente para determinar  $Z_o$ .

**Fig. 12.15** Circuito ac equivalente para determinar  $A_{\nu}$ .

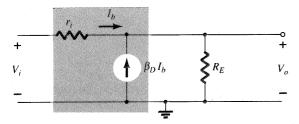

#### GANHO DE TENSÃO AC

O ganho de tensão ac para o circuito da Fig. 12.12 pode ser determinado usando-se o circuito ac equivalente da Fig. 12.15. Uma vez que

$$V_o = (I_b + \beta_D I_b) R_E = I_b (R_E + \beta_D R_E)$$

$$V_i = I_b r_i + (I_b + \beta_D I_b) R_E$$

das quais nós obtemos

e

$$V_i = I_b(r_i + R_E + \beta_D R_E)$$

tal que

$$V_o = \frac{V_i}{r_i + (R_E + \beta_D R_E)} (R_E + \beta_D R_E)$$

$$A_v = \frac{V_o}{V_i} = \frac{R_E + \beta_D R_E}{r_i + (R_E + \beta_D R_E)} \approx 1$$

(12.18)

## **EXEMPLO 12.10**

Calcule o ganho da tensão ac  $A_{\nu}$ , para o circuito da Fig. 12.12.

## Solução

$$A_{\nu} = \frac{390 \ \Omega + (8000)(390 \ \Omega)}{5 \ k\Omega + [390 \ \Omega + (8000)(390 \ \Omega)]} = \mathbf{0.998}$$

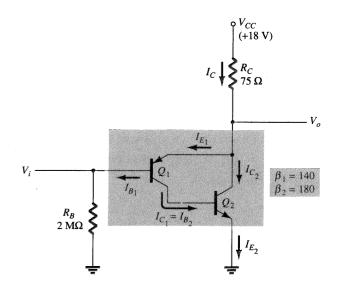

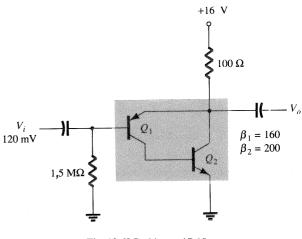

### 12.5 PAR REALIMENTADO

A conexão par realimentado (veja Fig. 12.16) é um circuito com dois transistores que opera com o circuito Darlington. Observe que o par realimentado usa um transistor *pnp*, excitando um transistor *npn*, sendo que os dois dispositivos atuam efetivamente como se fossem um transistor *pnp*. Da mesma forma que a conexão Dar-

Fig. 12.16 Conexão par realimentado.

Fig. 12.17 Operação do par realimentado.

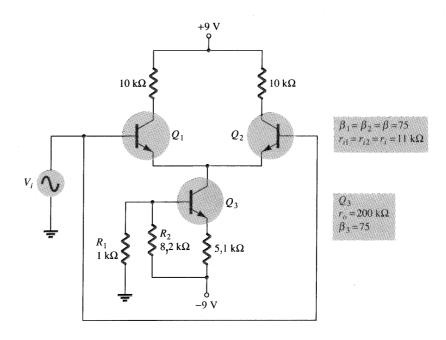

lington, o par realimentado fornece um ganho de corrente muito alto (o produto dos ganhos de corrente dos transistores). Uma aplicação típica (veja Cap. 16) usa uma conexão Darlington e um par realimentado para proporcionar operação complementar do transistor. A Fig. 12.17 apresenta um par realimentado utilizado na prática. Algumas considerações sobre a polarização de e a operação ac proporcionarão um melhor entendimento de como esta conexão trabalha.

## Polarização DC

Os cálculos de polarização de que se seguem usam simplificações para que se obtenham os resultados da forma mais simples possível. Da malha base-emissor de  $Q_1$ , obtém-se

$$V_{CC} - I_C R_C - V_{EB_1} - I_{B_1} R_B = 0$$

$$V_{CC} - \beta_1 \beta_2 I_{B_1} R_C - V_{EB_1} - I_{B_1} R_B = 0$$

A corrente de base é, então,

$$I_{B_1} = \frac{V_{CC} - V_{EB_1}}{R_B + \beta_1 \beta_2 R_C} \tag{12.19}$$

A corrente de coletor de  $Q_1$  é

$$I_{C_1} = \beta_1 I_{B_1} = I_{B_2}$$

a qual é também a corrente de base de  $Q_2$ . A corrente de coletor do transistor  $Q_2$  é

$$I_{C_2} = \beta_2 I_{B_2} \approx I_{E_2}$$

tal que a corrente através de  $R_C$  é

$$I_C = I_{E_1} + I_{C_2} \approx I_{C_1} + I_{C_2} \approx I_{C_2}$$

(12.20)

## **EXEMPLO 12.11**

Calcule as correntes e tensões de polarização para o circuito da Fig. 12.17 para que  $V_o$  seja metade da tensão da fonte de tensão  $(I_cR_c=9 \text{ V})$ .

## Solução

$$I_{B_1} = \frac{18 \text{ V} - 0.7 \text{ V}}{2 \text{ M}\Omega + (140)(180)(75 \Omega)} = \frac{17.3 \text{ V}}{3.89 \times 10^6} = 4.45 \mu\text{A}$$

A corrente de base de  $Q_2$  é, então

$$I_{B_2} = I_{C_1} = \beta_1 I_{B_1} = 140(4,45 \text{ } \mu\text{A}) = 0,623 \text{ } \text{mA}$$

resultando numa corrente de coletor de  $Q_2$  de

$$I_{C_2} = \beta_2 I_{B_2} = 180(0,623 \text{ mA}) = 112,1 \text{ mA}$$

e a corrente através de  $R_C$  é, então,

Eq. (12.20):

$$I_C = I_{E_1} + I_{C_2}$$

= 0,623 mA + 112,1 mA  $\approx I_{C_2}$  = 112,1 mA

A tensão de na saída é, portanto,

$$V_o(dc) = V_{CC} - I_C R_C = 18 \text{ V} - 112,1 \text{ mA}(75 \Omega) = 9,6 \text{ V}$$

$V_i(dc) = V_o(dc) - V_{BE} = 9,6 \text{ V} - 0,7 \text{ V} = 8,9 \text{ V}$

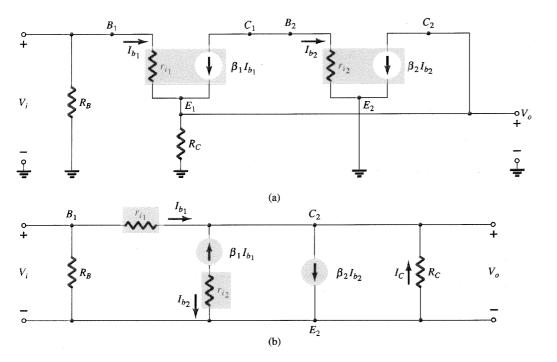

## Operação AC

O circuito equivalente ac para a Fig. 12.17 é desenhado na Fig. 12.18. O circuito é desenhado primeiro na Fig. 12.18a para mostrar claramente cada transistor e a posição dos resistores de base e coletor. O circuito equivalente ac é então redesenhado na Fig. 12.18b para permitir a análise.

### IMPEDÂNCIA DE ENTRADA AC, $Z_i$

A impedância de entrada ac vista olhando-se para dentro da base do transistor  $Q_1$  é determinada (refira-se à Fig. 12.18b) como se segue:

$$I_{b_1} = \frac{V_i - V_o}{r_i}$$

onde

$$V_o - -I_C R_C \approx (-\beta_1 I_{b_1} + \beta_2 I_{b_2}) R_C \approx (\beta_2 I_{b_2}) R_C$$

tal que

$$I_{b_1}r_{i_1} = V_i - V_o \approx V_i - \beta_2 I_{b_2} R_C$$

$$I_{b_1}r_{i_1} + \beta_2(\beta_1 I_{b_1}) R_C = V_i \quad \text{(desde que } I_{b_2} = I_{C_1} = \beta_1 I_{b_1})$$

$$\frac{V_i}{I_{b_1}} = r_{i_1} + \beta_1 \beta_2 R_C$$

Incluindo a resistência de polarização da base,

$$Z_i \approx R_B ||(r_{i_1} + \beta_1 \beta_2 R_C)||$$

(12.21)

## GANHO DE CORRENTE AC, $A_i$

O ganho de corrente ac pode ser determinado como se segue:

$$I_o = \beta_2 I_{b_2} - \beta_1 I_{b_1} - I_{b_1}$$

$$= \beta_2 (\beta_1 I_{b_1}) - (1 + \beta_1) I_{b_1} \approx \beta_1 \beta_2 I_{b_1}$$

$$\frac{I_o}{I_b} = \beta_1 \beta_2$$

Incluindo  $R_B$ , o ganho de corrente é

$$A_{i} = \frac{I_{o}}{I_{i}} = \frac{I_{o}}{I_{b_{1}}} \frac{I_{b_{1}}}{I_{i}} = \beta_{1}\beta_{2} \frac{R_{B}}{R_{B} + Z_{i}}$$

(12.22)

Fig. 12.18 Equivalente ac da Fig. 12.17

## IMPEDÂNCIA DE SAÍDA AC, $Z_o$

$Z_o$  pode ser obtida aplicando-se uma tensão,  $V_o$ , com  $V_i$  fixado em 0. A análise resultante fornece

$$Z_o = \frac{V_o}{I_o} = R_C ||r_{i_1}|| \frac{r_{i_1}}{\beta_1} || \frac{r_{i_1}}{\beta_1 \beta_2} \approx \frac{r_{i_1}}{\beta_1 \beta_2}$$

(12.23)

que representa uma baixa impedância de saída.

## GANHO DE TENSÃO AC, A,

A tensão de saída  $V_o$  é

$$V_o = -I_C R_C \approx \beta_1 \beta_2 I_{b_1} R_C$$

Uma vez que

$$I_{b_1} = \frac{V_i - V_o}{r_{i_1}}$$

$$V_o = V_i - I_{b_1} r_{i_1} = V_i - \frac{V_o}{\beta_1 \beta_2 R_C} r_{i_1}$$

$$A_{v} = \frac{V_{o}}{V_{i}} = \frac{1}{1 + r_{i}/(\beta_{1}\beta_{2}R_{C})} = \frac{\beta_{1}\beta_{2}R_{C}}{\beta_{1}\beta_{2}R_{C} + r_{i_{1}}}$$

(12.24)

## **EXEMPLO 12.12**

Calcule os valores ac  $Z_i$ ,  $Z_o$ ,  $A_i$ , e  $A_v$  para o circuito da Fig. 12.17. Assuma que  $r_i = 3 \text{ k}\Omega$ .

#### Solução

$$Z_i \approx R_B ||(r_{i_1} + \beta_1 \beta_2 R_C) = 2 M\Omega||[3 k\Omega + (140)(180)(75 \Omega)]|$$

$\approx 974 k\Omega$

$$A_i = \beta_1 \beta_2 \frac{R_B}{R_B + Z_i} = (140)(180) \left( \frac{2 \text{ M}\Omega}{2 \text{ M}\Omega + 974 \text{ k}\Omega} \right)$$

= 3.7 × 10<sup>6</sup>

Fig. 12.19 Circuito inversor CMOS.

$$Z_o \approx \frac{r_{i_1}}{\beta_1 \beta_2} = \frac{3 \times 10^3}{(140)(180)} = 0.12 \ \Omega$$

e

$$A_{\nu} = \frac{\beta_1 \beta_2 R_C}{\beta_1 \beta_2 R_C + r_{i_1}} = \frac{(140)(180)(75 \ \Omega)}{(140)(180)(75 \ \Omega) + 3000 \ \Omega}$$

$$= \mathbf{0.9984} \approx \mathbf{1}$$

O Exemplo 12.12 mostra que a conexão par realimentado proporciona uma operação com ganho de tensão muito próximo de 1 (tal como com a Darlington seguidor-de-emissor), um ganho de corrente muito alto, uma impedância de saída muito baixa, e uma alta impedância de entrada.

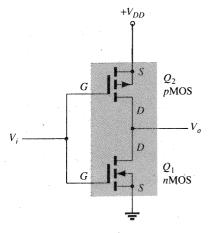

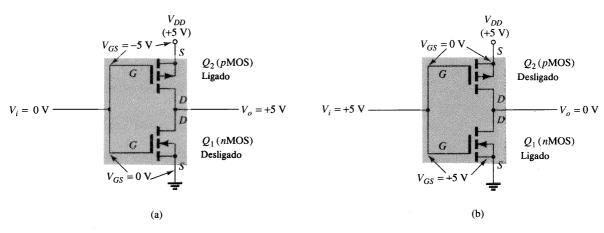

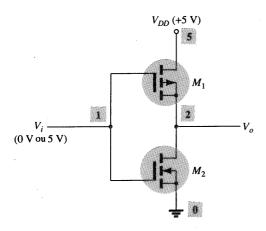

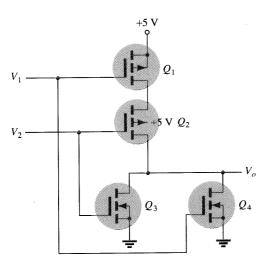

## 12.6 CIRCUITO CMOS

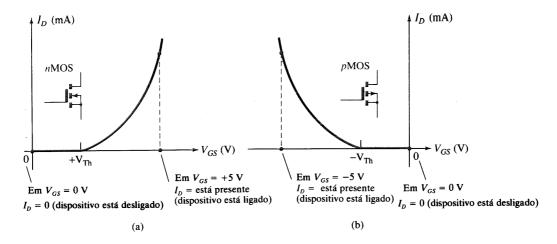

Um tipo de circuito muito utilizado em eletrônica digital utiliza os transistores MOSFET canal-p e canal-n (veja Fig. 12.19). Este MOSFET complementar ou circuito CMOS usa estes tipos de transistores opostos (ou complementares). A entrada,  $V_i$ , é aplicada a ambas as portas com a saída tomada do dreno, que está conectado a ambos. Antes de partirmos para a operação do circuito CMOS, vamos rever a operação do transistor MOSFET intensificação.

## Operação Ligado/Desligado do nMOS

A curva característica de dreno de um transistor MOSFET canal-n ou nMOS é mostrada na Fig. 12.20a. Com 0 V aplicado entre porta e fonte, não há corrente de dreno. Não haverá corrente até  $V_{GS}$  ser elevado além do nível de limiar do dispositivo,  $V_T$ , quando então surgirá uma corrente. Com uma entrada de, digamos, +5 V, o dispositivo nMOS está completamente ligado com uma corrente  $I_D$  presente. Em resumo:

Uma entrada de 0 V deixa os nMOS desligado, enquanto uma entrada de +5 V liga o nMOS.

## Operação Ligado/Desligado do pMOS

A curva característica do dreno para um transistor MOSFET canal-pMOS é mostrada na Fig. 12.20b. Quando 0 V é aplicado, o dispositivo está desligado (nenhuma corrente de dreno presente), enquanto para uma entrada de -5 V (maior que a tensão de limiar), o dispositivo está ligado com corrente de dreno presente. Em resumo:

$V_{GS} = 0 V deixa o pMOS desligado; V_{GS} = -5 V liga o pMOS.$

## Operação do Circuito CMOS

Considere, em seguida, como o circuito CMOS real da Fig. 12.21 opera com uma entrada de 0~V ou entrada de +5~V.

## **ENTRADA 0-V**

Quando 0 V é aplicado como entrada ao circuito CMOS, surge uma tensão de 0 V em nMOS e pMOS. A Fig. 12.21a mostra que

Fig. 12.20 Curva característica do MOSFET mostrando as condições ligado/desligado: (a) nMOS; (b) pMOS.

Para *n*MOS

$$(Q_1)$$

:  $V_{GS} = V_i - 0 \text{ V} = 0 \text{ V} - 0 \text{ V} = 0 \text{ V}$

Para pMOS

$$(Q_2)$$

:  $V_{GS} = V_i - (+5 \text{ V}) = 0 \text{ V} - 5 \text{ V} = -5 \text{ V}$

Uma entrada de 0 V para um transistor nMOS  $Q_1$  deixa este dispositivo desligado. A mesma entrada de 0 V, entretanto, resulta numa tensão porta-fonte, de um transistor pMOS, de -5 V (porta em 0 V é 5 V menor que a fonte em +5 V), ligando este dispositivo. A saída,  $V_o$ , é então +5 V.

## ENTRADA +5-V

Quando  $V_i = +5$  V, esta tensão aparece em ambas as portas. A Fig. 12.21b mostra que

Para *n*MOS (

$$Q_1$$

):  $V_{GS} = V_i - 0 \text{ V} = +5 \text{ V} - 0 \text{ V} = +5 \text{ V}$

Para pMOS

$$(Q_2)$$

:  $V_{GS} = V_i - (+5 V) = +5 V - 5 V = 0 V$

Esta entrada mantém o transistor  $Q_1$  ligado e o transistor  $Q_2$  desligado, com a saída próxima de 0 V no transistor em condução  $Q_2$ . A conexão CMOS da Fig. 12.19 opera como um inversor lógico com  $V_o$  sendo o oposto de  $V_i$ , como mostrado no Quadro 12.1.

| QUADRO 12.1 Operação do Circuito CMOS |                     |                     |                                |  |

|---------------------------------------|---------------------|---------------------|--------------------------------|--|

| $V_1(V)$                              | $Q_1$               | $Q_2$               | $V_{o}\left(\mathbf{V}\right)$ |  |

| 0<br>+5                               | Desligado<br>Ligado | Ligado<br>Desligado | +5                             |  |

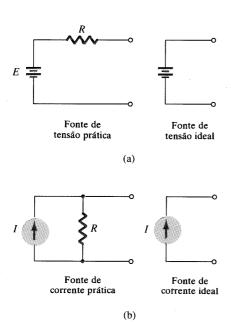

## 12.7 CIRCUITOS DE FONTES DE CORRENTE

O conceito de uma fonte de potência fornece um impulso inicial em nossas considerações de circuitos de fonte de corrente. Uma fonte de tensão prática (veja Fig. 12.22a) é uma fonte de tensão em série com uma resistência. Uma fonte de tensão ideal tem R=0, enquanto uma fonte prática inclui uma pequena resistência. Uma fonte de corrente na prática (veja Fig. 12.22b) é uma fonte de corrente em paralelo com uma resistência. Uma fonte de corrente ideal tem  $R=\infty$ , enquanto uma fonte de corrente na prática inclui uma resistência muito grande.

Uma fonte de corrente ideal fornece uma corrente constante, sem se importar com a carga conectada a ela. Em eletrônica, um circuito que fornece uma corrente constante com uma impedân-

Fig. 12.21 Operação do circuito CMOS: (a) saída +5 V; (b) saída 0 V.

Fig. 12.22 Fontes de tensão e corrente.

cia muito alta é bastante utilizado. Circuitos de corrente constante podem ser construídos usando dispositivos FET, dispositivos bipolares e uma combinação destes componentes. Há circuitos usados em forma discreta e outros mais adequados para operação em circuitos integrados. Consideramos algumas formas de ambos os tipos nesta seção e na Seção 12.8.

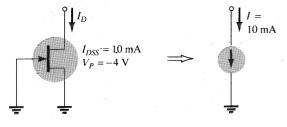

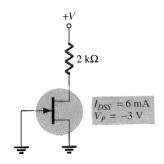

## Fonte de Corrente a JFET

Uma fonte de corrente simples com JFET é mostrada na Fig. 12.23. Com  $V_{GS}$  fixado em 0 V, a corrente de dreno é fixada em

$$I_D = I_{DSS} = 10 \text{ mA}$$

O dispositivo, portanto, opera tal como uma fonte de corrente de valor 10 mA. Enquanto o JFET real tem uma resistência de saída, a fonte de corrente ideal seria uma fonte de 10 mA, como mostrado na Fig. 12.23.

Fig. 12.23 Fonte de corrente constante a JFET.

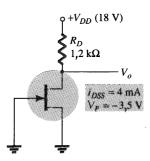

### **EXEMPLO 12.13**

Determine a corrente de carga  $I_D$  e a tensão de saída  $V_o$  para o circuito da Fig. 12.24, para:

(a)

$$R_{\rm p} = 1.2 \, {\rm k}\Omega$$

(a)

$$R_D = 1.2 \text{ k}\Omega$$

(b)  $R_D = 3.3 \text{ k}\Omega$

Fig. 12.24 Fonte de corrente a JFET para o Exemplo 12.13.

## Solução

Uma vez que

$$V_{GS}=0$$

V,  $I_D=I_{DSS}=4$  mA.

(a)  $V_o=V_{DD}-I_DR_D=18$  V  $-(4$  mA) $(1,2$  k $\Omega)=13,2$  V

(b)  $V_o=V_{DD}-I_DR_D=18$  V  $-(4$  mA) $(3,3$  k $\Omega)=4,8$  V

Note que a tensão de saída varia com  $R_D$ , mas a corrente através de  $R_D$  permanece 4 mA, uma vez que o JFET opera como uma fonte de corrente constante.

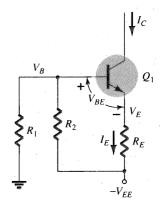

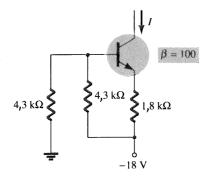

## Fonte de Corrente Constante com Transistor **Bipolar**

Transistores bipolares podem ser conectados de várias maneiras em um circuito que atua como uma fonte de corrente constante. A Fig. 12.25 mostra um circuito, usando alguns resistores e um transistor npn operando como uma fonte de corrente constante. A corrente através de  $I_E$  pode ser determinada como segue. Assumindo que a impedância de entrada da base é muito maior que  $R_1$  ou  $R_2$ ,

$$V_B = \frac{R_1}{R_1 + R_2} \left( -V_{EE} \right)$$

$$V_E = V_B - 0.7 \text{ V}$$

$I_E = \frac{V_E - (-V_{EE})}{R_E} \approx I_C$  (12.25)

com

onde  $I_C$  é a corrente constante fornecida pelo circuito da Fig. 12.25.

Fig. 12.25 Fonte de corrente constante discreta.

## Ą

## **EXEMPLO 12.14**

Calcule a corrente constante  $I_C$  no circuito da Fig. 12.26.

Fig. 12.26 Fonte de corrente constante para o Exemplo 12.14.

### Solução

$$V_B = \frac{R_1}{R_1 + R_2} (-V_{EE}) = \frac{5.1 \text{ k}\Omega}{5.1 \text{ k}\Omega + 5.1 \text{ k}\Omega} (-20 \text{ V})$$

$$= -10 \text{ V}$$

$$V_E = V_B - 0.7 \text{ V} = -10 \text{ V} - 0.7 \text{ V} = -10.7 \text{ V}$$

$$I = I_E = \frac{V_E - (-V_{EE})}{R_E} = \frac{-10.7 \text{ V} - (-20 \text{ V})}{2 \text{ k}\Omega}$$

$$= \frac{9.3 \text{ V}}{2 \text{ k}\Omega} = 4.65 \text{ mA}$$

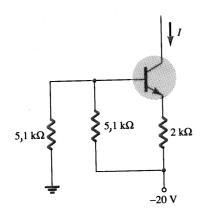

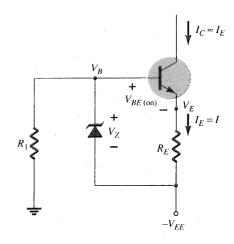

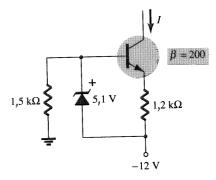

## Fonte de Corrente Constante a Transistor/Zener

Substituindo o resistor  $R_2$  por um diodo Zener, como mostrado na Fig. 12.27, obtemos uma fonte de corrente constante melhor do que a da Fig. 12.25. O diodo Zener resulta em uma corrente constante calculada usando a equação LTK (Lei das Tensões de Kirchhoff) base-emissor. O valor de I pode ser calculado usando

$$I \approx I_E = \frac{V_Z - V_{BE}}{R_E} \tag{12.26}$$

O principal ponto a considerar é que a corrente constante depende da tensão sobre o diodo Zener, a qual permanece razoavelmente constante, e do resistor-de-emissor  $R_E$ . A fonte de tensão  $V_{EE}$  não tem efeito sobre o valor de I.

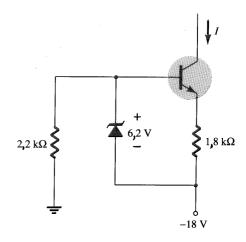

## **EXEMPLO 12.15**

Calcule a corrente constante *I* no circuito da Fig. 12.28.

## Solução

Eq. (12.26):

$$I = \frac{V_Z - V_{BE}}{R_E}$$

Fig. 12.27 Circuito de corrente constante usando diodo Zener.

Fig. 12.28 Circuito de corrente constante para o Exemplo 12.15.

$$= \frac{6.2 \text{ V} - 0.7 \text{ V}}{1.8 \text{ k}\Omega}$$

$$= 3.06 \text{ mA} \approx 3 \text{ mA}$$

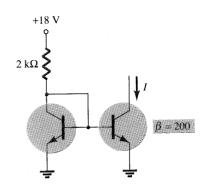

## 12.8 CIRCUITOS ESPELHOS DE CORRENTE

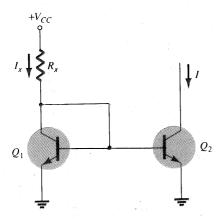

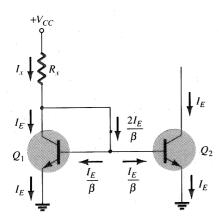

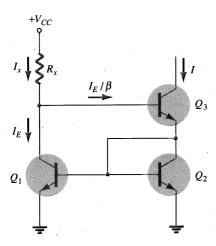

Um circuito espelho de corrente (veja Fig. 12.29) fornece uma corrente constante e é usado principalmente em circuitos integrados. A corrente constante é obtida a partir de uma corrente de saída que é o reflexo ou espelho de uma corrente desenvolvida sobre um lado do circuito. O circuito é particularmente apropriado na fabricação de CIs, uma vez que requer que os transistores usados tenham quedas de tensão base-emissor idênticas e idênticos valores de beta — conseguem-se resultados melhores quando os transistores são formados ao mesmo tempo na fabricação do CI. Na Fig. 12.29, a corrente  $I_x$ , estabelecida pelo transistor  $Q_1$  e pelo resistor  $R_x$  é refletida na corrente I através do transistor  $Q_2$ .

As correntes  $I_X$  e I podem ser obtidas usando as correntes de circuito listadas na Fig. 12.30. Assumimos que a corrente de emissor ( $I_E$ ) para ambos os transistores é a mesma ( $Q_1$  e  $Q_2$  foram fabri-

Fig. 12.29 Circuito espelho de corrente.

cados próximo um do outro no mesmo chip). As correntes de base dos dois transistores são, então, aproximadamente

$$I_B = \frac{I_E}{\beta + 1} \approx \frac{I_E}{\beta}$$

A corrente de coletor para cada transistor é então

$$I_{\rm C} \approx I_{\rm E}$$

Finalmente, a corrente através do resistor  $R_x$ ,  $I_x$  é

$$I_X = I_E + \frac{2I_E}{\beta} = \frac{\beta I_E}{\beta} + \frac{2I_E}{\beta} = \frac{\beta + 2}{\beta} I_E \approx I_E$$

Em resumo, a corrente constante fornecida no coletor de  $Q_2$  reflete a corrente de  $Q_1$ . Uma vez que

$$I_X = \frac{V_{CC} - V_{BE}}{R_X} \tag{12.27}$$

a corrente  $I_X$  estabelecida por  $V_{CC}$  e  $R_X$  é refletida na corrente do coletor de  $Q_2$ .

O transistor  $Q_1$  atua como um diodo porque a base e coletor estão em curto.

Fig. 12.30 Correntes para o circuito espelho de corrente.

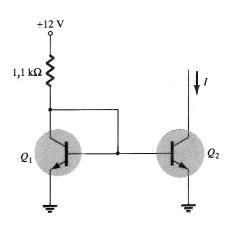

### **EXEMPLO 12.16**

Calcule a corrente refletida, *I*, no circuito da Fig. 12.31.

Fig. 12.31 Circuito espelho de corrente para o Exemplo 12.16.

#### Solução

Eq. (12.27):

$$I = I_X = \frac{V_{CC} - V_{BE}}{R_X} = \frac{12 \text{ V} - 0.7 \text{ V}}{1.1 \text{ k}\Omega}$$

= **10.27 mA**

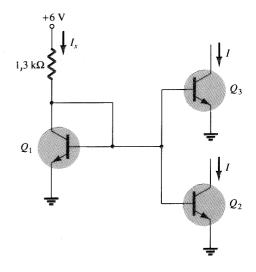

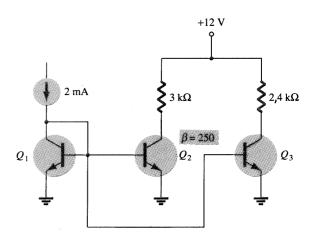

## **EXEMPLO 12.17**

Calcule a corrente, I, através de cada um dos transistores  $Q_2$  e  $Q_3$  no circuito da Fig. 12.32.

Fig. 12.32 Circuito espelho de corrente para o Exemplo 12.17.

#### Solução

A corrente  $I_x$  é

$$I_X = I_E + \frac{3I_E}{\beta} = \frac{\beta + 3}{\beta}I_E \approx I_E$$

**Portanto**

$$I \approx I_X = \frac{V_{CC} - V_{BE}}{R_X} = \frac{6 \text{ V} - 0.7 \text{ V}}{1.3 \text{ k}\Omega} = 4.08 \text{ mA}$$

Fig. 12.33 Circuito espelho de corrente com impedância de saída mais alta.

Fig. 12.34 Conexão espelho de corrente.

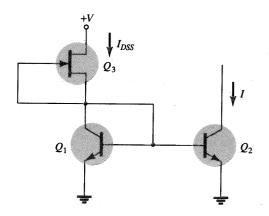

A Fig. 12.33 mostra uma outra forma de espelho de corrente. Neste circuito, a impedância de saída é mais alta do que a do circuito da Fig. 12.29. A corrente através de  $R_X$  é

$$I_X = \frac{V_{CC} - 2V_{BE}}{R_X} \approx I_E + \frac{I_E}{\beta} = \frac{\beta + 1}{\beta} I_E \approx I_E$$

$$I \approx I_E = I_X$$

Novamente, vemos que a corrente de saída I é um valor refletido da corrente que passa pelo resistor  $R_x$ .

A Fig. 12.34 mostra ainda uma outra forma de espelho de corrente. O JFET fornece uma corrente constante indicada pelo valor de  $I_{DSS}$ . Esta corrente é refletida, resultando numa corrente através de  $Q_2$  do mesmo valor:

$$I = I_{DSS}$$

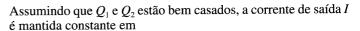

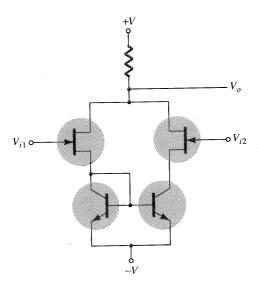

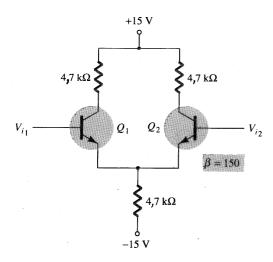

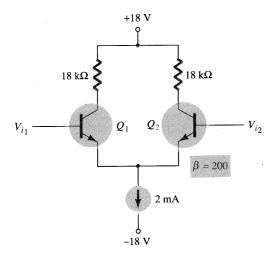

## 12.9 CIRCUITO AMPLIFICADOR DIFERENCIAL

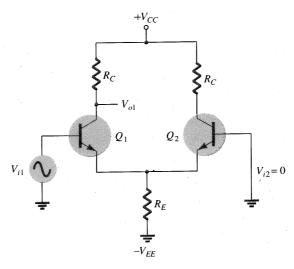

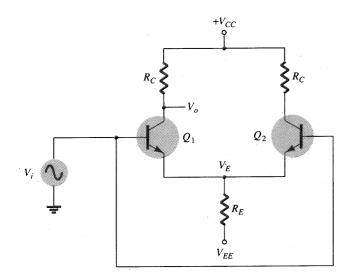

O circuito amplificador diferencial é uma conexão extremamente popular usada em unidades de CIs. Esta conexão pode ser descrita considerando o amplificador diferencial básico mostrado na Fig. 12.35. Note que o circuito tem duas entradas separadas, duas saídas separadas, e que os emissores estão conectados um ao outro. Apesar de muitos circuitos amplificadores diferenciais utilizarem duas fontes de tensão separadas, o circuito pode operar também usando uma única fonte de tensão.

Algumas combinações de sinais de entrada são possíveis.

Se um sinal de entrada é aplicado numa entrada, com a outra entrada conectada à terra, a operação é denominada *terminação simples*.

Se dois sinais de entrada de polaridades opostas são aplicados, a operação é denominada *terminação dupla*.

Se um mesmo sinal de entrada é aplicado a ambas as entradas, a operação é chamada *modo comum*.

Na operação com terminação simples, um único sinal de entrada é aplicado. Entretanto, como os emissores estão conectados, o sinal de entrada aciona ambos os transistores, resultando em saídas para *ambos* os coletores.

Na operação com terminação dupla, dois sinais de entrada são aplicados. A diferença entre as amplitudes dos sinais de entradas produz dois sinais de saída nos coletores dos transistores.

Na operação modo comum, o sinal comum de entrada produz dois sinais de polaridade oposta em cada coletor que se cancelam na saída. No entanto, o que se verifica na prática é que os

Fig. 12.35 Circuito amplificador diferencial básico.

Fig. 12.36 Polarização de do circuito amplificador diferencial.

dois sinais opostos não possuem exatamente a mesma amplitude, e, quando somados, não se cancelam completamente.

A característica principal do amplificador diferencial é o ganho muito grande quando sinais opostos são aplicados às entradas, comparado a um ganho muito pequeno resultante de entradas comuns. A razão entre este ganho diferencial e o ganho comum é chamado *rejeição de modo comum*. Estes conceitos serão discutidos completamente no Cap. 14. Por enquanto, vamos nos restringir à operação do circuito amplificador diferencial.

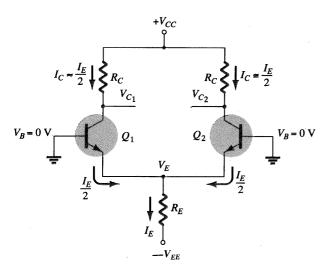

## Polarização DC

Vamos considerar primeiro a operação de polarização de do circuito da Fig. 12.35. Com as entradas ac obtidas das fontes de tensão, pode-se considerar que a tensão de em cada entrada é 0 V, como mostrado na Fig. 12.36. Com cada tensão de base em 0 V, a tensão de polarização de no emissor-comum é

$$V_E = 0 \text{ V} - V_{BE} = -0.7 \text{ V}$$

A corrente de polarização de do emissor é então

$$I_E = \frac{V_E - (-V_{EE})}{R_E} \approx \frac{V_{EE} - 0.7 \text{ V}}{R_E}$$

(12.28)

Assumindo que os transistores são bem casados (como ocorreria numa unidade de CI).

$$I_{C_1} = I_{C_2} = \frac{I_E}{2} \tag{12.29}$$

resultando numa tensão de coletor de

$$V_{C_1} = V_{C_2} = V_{CC} - I_C R_C = V_{CC} + \frac{I_E}{2} R_C$$

(12.30)

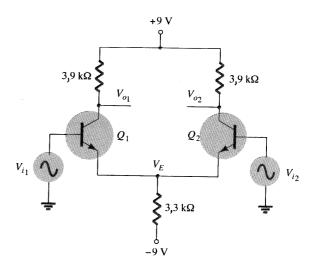

## **EXEMPLO 12.18**

Calcule as tensões e correntes de no circuito da Fig. 12.37.

## Solução

Eq. (12.28):

$$I_E = \frac{V_{EE} - 0.7 \text{ V}}{R_E} = \frac{9 \text{ V} - 0.7 \text{ V}}{3.3 \text{ k}\Omega} \approx 2.5 \text{ mA}$$

Fig. 12.37 Circuito amplificador diferencial para o Exemplo 12.18.

A corrente de coletor é, então,

Eq. (12.29):

$$I_C = \frac{I_E}{2} = \frac{2,5 \text{ mA}}{2} = 1,25 \text{ mA}$$

resultando numa tensão de coletor de

Eq. (12.30):

$$V_C = V_{CC} - I_C R_C$$

= 9 V - (1.25 mA)(3.9 k $\Omega$ )  $\approx$  **4.1** V

A tensão comum de emissor é, portanto,  $-0.7~\rm V$ , enquanto a tensão de polarização do coletor está próxima de 4,1 V para ambas as saídas.

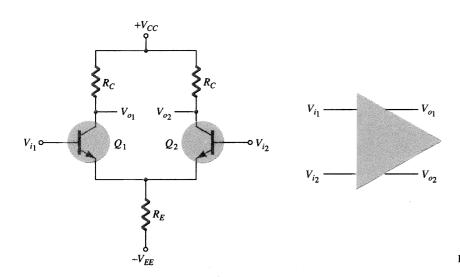

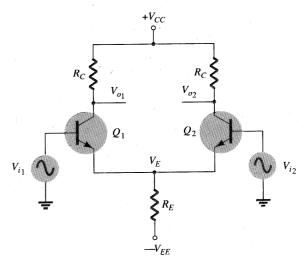

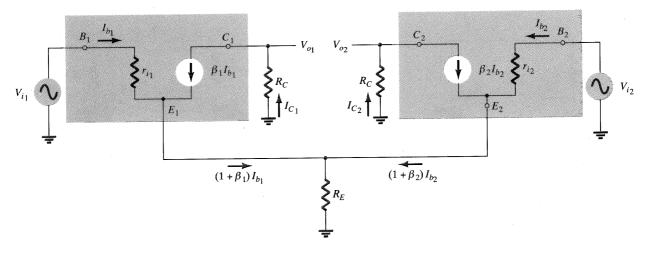

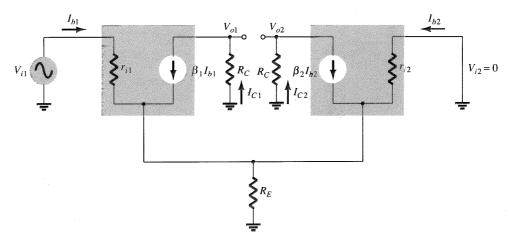

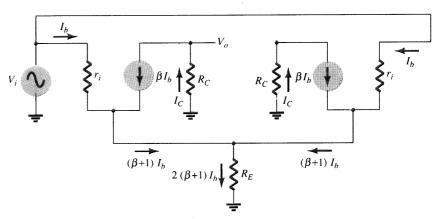

## Operação AC do Circuito

Uma conexão ac de um amplificador diferencial é mostrada na Fig. 12.38. Sinais de entrada separados são aplicados,  $V_{i_1}$  e  $V_{i_2}$ , resultando em saídas separadas,  $V_{o_1}$  e  $V_{o_2}$ . Para realizar a análise, o circuito é redesenhado na Fig. 12.39. Cada transistor é substituído por seu equivalente ac.

Fig. 12.38 Conexão ac do amplificador diferencial.

Fig. 12.39 Equivalente ac do circuito amplificador diferencial.

Fig. 12.40 Conexão para calcular  $A_{v_1} = V_{o_1} / V_{i_1}$ .

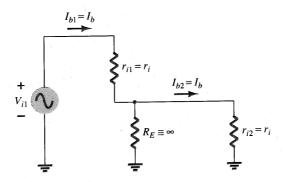

## GANHO DE TENSÃO AC COM TERMINAÇÃO SIMPLES

Para calcular o ganho de tensão ac  $V_o/V_i$  com terminação simples aplica-se um sinal para uma entrada com a outra conectada à terra, como mostrado na Fig. 12.40. O equivalente ac desta conexão é desenhado na Fig. 12.41. A corrente de base ac pode ser calculada usando a equação LTK (Lei das Tensões de Kirchhoff) da entrada da base 1. Se assumirmos que os dois transistores são bem casados, então

$$I_{b_1} = I_{b_2} = I_b$$

$r_{i_1} = r_{i_2} = r_i$

Com  $R_E$  muito grande (idealmente infinito), o circuito para obtenção da equação LTK simplifica-se para o da Fig. 12.42, do qual podemos escrever

$$V_{i_1} - I_b r_i - I_b r_i = 0$$

$$I_b = \frac{V_{i_1}}{2r_i}$$

Se nós assumirmos também que

$$\beta_1 = \beta_2 = \beta$$

então

$$I_C = \beta I_b = \beta \frac{V_{i_1}}{2r_i}$$

e a amplitude da tensão de saída em qualquer coletor é

$$V_o = I_C R_C = \beta \frac{V_{i_1}}{2r_1} R_C = \frac{\beta R_C}{2\beta r_e} V_i$$

para o qual o ganho de tensão com terminação simples em qualquer coletor é

$$A_{v} = \frac{V_{o}}{V_{i}} = \frac{R_{C}}{2r_{e}}$$

(12.31)

Fig. 12.41 Equivalente ac do circuito da Fig. 12.40.

Fig. 12.42 Circuito parcial para calcular  $I_b$ .

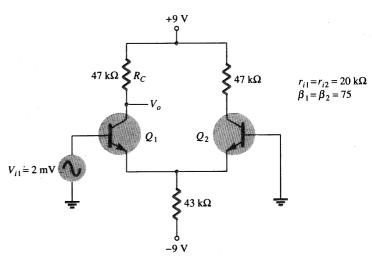

## **EXEMPLO 12.19**

Calcule a tensão de saída com terminações simples,  $V_{o_1}$ , para o circuito da Fig. 12.43.

## Solução

Os cálculos de polarização de fornecem

$$I_E = \frac{V_{EE} - 0.7 \text{ V}}{R_E} = \frac{9 \text{ V} - 0.7 \text{ V}}{43 \text{ k}\Omega} = 193 \text{ } \mu\text{A}$$

A corrente de de coletor é então

$$I_C = \frac{I_E}{2} = 96,5 \ \mu A$$

tal que

$$V_C = V_{CC} - I_C R_C = 9 \text{ V} - (96.5 \ \mu\text{A})(47 \text{ k}\Omega) = 4.5 \text{ V}$$

O valor de  $r_e$  é

$$r_e = \frac{26}{0.0965} \cong 269 \ \Omega$$

A amplitude do ganho de tensão ac pode ser calculada usando a Eq. (12.31):

$$A_{v} = \frac{R_{C}}{2r_{e}} = \frac{(47 \text{ k}\Omega)}{2(269 \Omega)} = 87.4$$

proporcionando uma amplitude de tensão ac de saída

$$V_o = A_v V_i = (87.4)(2 \text{ mV}) = 174.8 \text{ mV} = 0.175 \text{ V}$$

Fig. 12.43 Circuito para os Exemplos 12.19 e 12.20.

Fig. 12.44 Conexão modo comum.

## GANHO DE TENSÃO AC COM TERMINAÇÃO DUPLA

Uma análise semelhante pode ser usada para mostrar que para a condição em que sinais são aplicados em ambas as entradas, a amplitude do ganho de tensão diferencial seria

$$A_d = \frac{V_o}{V_d} = \frac{\beta R_C}{2r_i} \tag{12.32}$$

onde  $V_d = V_{i_1} - V_{i_2}$ .

## Operação Modo Comum do Circuito

Um amplificador diferencial produz uma grande amplificação da diferença entre os níveis aplicados nas entradas. No entanto, quando o mesmo sinal é aplicado em ambas as entradas, verifica-se na saída uma pequena amplificação deste sinal. Uma conexão ac mostrando uma entrada comum a ambos os transistores é mostrada na Fig. 12.44. O circuito ac equivalente é então desenhado na Fig. 12.45, do qual podemos escrever

$$I_b = \frac{V_i - 2(\beta + 1)I_b R_E}{r_i}$$

a qual pode ser reescrita como

$$I_b = \frac{V_i}{r_i + 2(\beta + 1)R_E}$$

A amplitude da tensão de saída é, então,

$$V_o = I_C R_C = \beta I_b R_C = \frac{\beta V_i R_C}{r_i + 2(\beta + 1)R_E}$$

fornecendo uma amplitude do ganho de tensão de

$$A_c = \frac{V_o}{V_i} = \frac{\beta R_C}{r_i + 2(\beta + 1)R_E}$$

(12.33)

### **EXEMPLO 12.20**

Calcule o ganho em modo comum para o circuito amplificador da Fig. 12.43.

### Solução

Eq. (12.33):

$$A_c = \frac{V_o}{V_i} = \frac{\beta R_C}{r_i + 2(\beta + 1)R_E}$$

$$= \frac{75(47 \text{ k}\Omega)}{20 \text{ k}\Omega + 2(76)(43 \text{ k}\Omega)} = \mathbf{0.54}$$

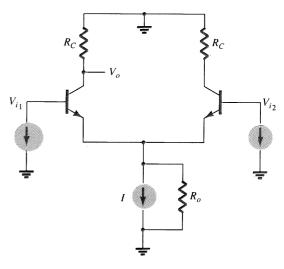

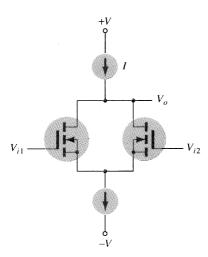

## Uso de Fonte de Corrente Constante

Um bom amplificador diferencial tem um ganho diferencial muito grande,  $A_d$ , o qual é muito maior que o ganho em modo comum,  $A_c$ . A rejeição de modo comum do circuito pode ser consideravelmente melhorada fazendo o ganho em modo comum tão pequeno quanto possível (idealmente, 0). Da Eq. (12.33), vemos que, quanto maior  $R_E$ , menor  $A_C$ . Um método bastante utilizado para aumentar o valor ac de  $R_E$  é usar um circuito com fonte de corrente constante. A Fig. 12.46 mostra um amplificador diferencial com fonte de corrente constante para fornecer um alto valor de resistência do emissor comum para o terra ac. A melhoria implementada por este circuito em relação ao da Fig. 12.35 é justamente o fato de estabelecer uma impedância ac muito grande para  $R_E$  através da fonte de corrente constante. A Fig. 12.47 mostra o circuito

Fig. 12.45 Circuito ac em conexão modo comum.

Fig. 12.46 Amplificador diferencial com fonte de corrente constante.

equivalente ac para o circuito da Fig. 12.46. Uma fonte de corrente constante na prática é representada por uma alta impedância, em paralelo com uma fonte de corrente.

### EXEMPLO 12.21

Calcule o ganho em modo comum para o amplificador diferencial da Fig. 12.48.

### Solução

Usando  $R_E = r_o = 200 \text{ k}\Omega$ , temos

Fig. 12.47 Equivalente ac do circuito da Fig. 12.46.

$$A_c = \frac{\beta R_C}{r_i + 2(\beta + 1)R_E} = \frac{75(10 \text{ k}\Omega)}{11 \text{ k}\Omega + 2(76)(200 \text{ k}\Omega)}$$

$$= 24.7 \times 10^{-3}$$

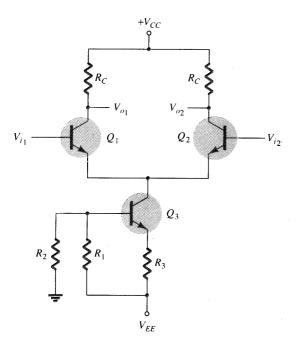

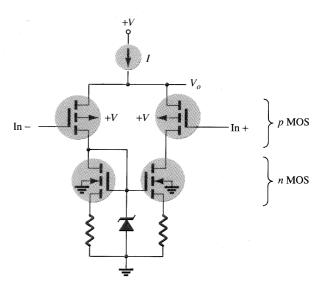

## 12.10 CIRCUITOS AMPLIFICADORES DIFERENCIAIS BIFET, BIMOS E CMOS

Embora a seção anterior tenha apresentado os amplificadores diferenciais usando dispositivos bipolares, algumas unidades comercialmente disponíveis também usam transistores JFET e MOSFET para construir estes tipos de circuito. Uma unidade de CI contendo um amplificador diferencial construído usando transistores bipolar (Bi) e de efeito de campo (FET) é denominado como um *circuito BiFET*. Uma unidade de CI feita usando transistores de como um circuito BiFET.

Fig. 12.48 Circuito para o Exemplo 12.21.

Fig. 12.49 Circuito amplificador diferencial BiFET.

Fig. 12.51 Amplificador diferencial CMOS.

sistores bipolar (Bi) e MOSFET (MOS) é chamada de *circuito BiMOS*. Finalmente, um circuito construído usando transistores MOSFET de tipos opostos é um *circuito CMOS*.

Os circuitos usados para mostrar os vários circuitos multidispositivos são, na verdade, simbólicos. Os circuitos reais usados em CIs são muito mais complexos. A Fig. 12.49 mostra um circuito BiFET com transistores JFET nas entradas e transistores bipolares que atuam como fonte de corrente (usando um circuito espelho de corrente). O espelho de corrente assegura que cada JFET está operando com a mesma corrente de polarização. Para operação ac o JFET fornece uma alta impedância de entrada (muito maior que a fornecida usando somente transistores bipolares).

A Fig. 12.50 mostra um circuito usando transistores de entrada MOSFET e transistores bipolares para fontes de corrente. A unidade BiMOS apresenta uma impedância de entrada mais alta que o BiFET, devido ao uso de transistores MOSFET.

Finalmente, um circuito amplificador diferencial pode ser construído usando transistores MOSFET complementares como

mostrado na Fig. 12.51. Os transistores *p*MOS fornecem entradas opostas, enquanto os transistores *n*MOS operam como fontes de corrente constante. Uma única saída é tomada do ponto comum entre os transistores *n*MOS e *p*MOS sobre um lado do circuito. Este tipo de amplificador CMOS é particularmente adequado para operação com pilhas devido à sua baixa dissipação de potência.

## 12.11 ANÁLISE POR COMPUTADOR

A análise por computador de vários circuitos compostos pode ser facilmente obtida usando-se o programa PSpice. Pode-se descrever ainda os circuitos separadamente — mas alguns poucos minutos devem ser suficientes para se obter uma listagem do circuito e os resultados desejados.

Algumas linhas do programa PSpice são necessárias para especificar os detalhes da análise ac desejada.

Para especificar o sinal ac de entrada:

VI N1 N2 AC VOLTAGE

p. ex.

VI 1 2 AC 10MV  $V_i = 10 \text{ mV (ac)}$

Para especificar a frequência do sinal de entrada:

.AC LIN NS FS FE

p. ex.

.AC LIN 1 10KH 10KH  $(f_i = 10 \text{ kHz})$

Para especificar a saída ac: Tendo-se pedido a análise ac, pode-se incluir uma listagem das tensões e correntes ac desejadas. A forma de pedir esta listagem é

.PRINT AC VOLTAGE\_LIST

p. ex.

.PRINT AC V(1) V(6) I(RD) V(3,4)

Fig. 12.50 Circuito amplificador diferencial BiMOS.

#### **MODEL LINES**

1. Para um dispositivo TBJ, a linha de modelo inclui o dispositivo beta.

.MODEL DEV\_NAME NPN (BF =  $\_$ ) p. ex.

.MODEL TRAN1 NPN (BF = 200)

2. Para um dispositivo JFET, a linha de modelo inclui  $V_P$  e  $I_{DSS}$ . MODEL DEV\_NAME NJF VTO = \_\_\_\_\_ BETA = \_\_\_\_ p. ex.

.MODEL FET3 NJF VTO = -4 BETA = 0,625E-3 JFET canal-n: VTO =  $V_p$  = -4V, BETA =  $I_{DSS}/V_p^2$ , tal que  $I_{DSS}$  = 10 mA,

3. Para um MOSFET, a linha de modelo inclui  $V_T$ .

.MODEL DEV\_\_NAME PMOS or NMOS (VTO = \_\_\_\_)

p. ex.

.MODEL MOSA PMOS (VTO = -2V) pMOS com  $V_T = -2V$

## Programa 12.1. Amplificador a JFET em Cascata

Uma listagem do PSpice para fazer a análise do amplificador a JFET em cascata da Fig. 12.2 é fornecida na Fig. 12.52; veja a Fig. 12.53 para o circuito, mostrando todos os nós usados. Observe que na listagem do PSpice, a fonte de tensão, resistores e capacitores são descritos primeiro. Uma carga de  $R_L=1~\mathrm{M}\Omega$  é adicionada para estabelecer a malha de saída do circuito entre o capacitor e o terra. Os dois JFETs vistos são do mesmo modelo, e têm valores especificados de

$$VTO = V_P = -4 \text{ V}, e I_{DSS} = 10 \text{ mA (de BETA} = 0.625 \text{ E-6})$$

O sinal ac de entrada é  $V_i=10~\rm mV$  em  $f=10\rm kHz$ . A linha .OP é inserida para que seja informado o ponto de operação — valores de polarização de e parâmetros de operação do transistor. A saída também fornece uma listagem das tensões ac na entrada e na saída de cada estágio. Um resumo dos resultados é dado em seguida.

Resultados da polarização dc (para cada transistor):

$$V_G \approx 0 \text{ V}, \qquad V_D \approx 13.3 \text{ V}, \qquad V_S \approx 1.9 \text{ V}$$

```

Cascade JFET Amplifier

CIRCUIT DESCRIPTION

VDD 8 0 20V

RG1 2 0 3.3MEG

RD1 3 8 2.4K

RS1 4 0 680

CS1 4 0 100UF

C1 1 2 0.05UF

C2 3 5 0.05UF

RG2 5 0 3.3MEG

RD2 6 8 2.4K

RS2 7 0 680

CS2 7 0 100UF

C3 6 9 0.05UF

RL 9 0 1MEG

J1 3 2 4 NFET

J2 6 5 7 NFET

.MODEL NFET NJF VTO=-4V BETA=0.625E-3

VI 1 0 AC 10MV

.AC LIN 1 10KH 10KH

PRINT AC V(1) V(3) V(6) V(9) OPTIONS NOPAGE

Junction FET MODEL PARAMETERS

NJF

-4

VTO

BETA 625.000000E-06

27,000 DEG C

SMALL SIGNAL BIAS SOLUTION

TEMPERATURE =

NODE

VOLTAGE

TAGE NODE VOLTAGE

0.0000 ( 2) 50.28E-06

NODE

VOLTAGE

NODE

VOLTAGE

1)

3)

13.3270

4)

1.8908

50.28E-06

13.3270

1.8908

9)

0.0000

VOLTAGE SOURCE CURRENTS

CURRENT

-5.561E-03

TOTAL POWER DISSIPATION

1.11E-01 WATTS

OPERATING POINT INFORMATION

**** JFETS

NAME

NFET

NFET

MODEL

2.78E-03

ID

2.78E-03

-1.89E+00

-1.89E+00

VGS

1.14E+01

VDS

1.14E+01

GM

2.64E-03

2.64E-03

TEMPERATURE =

27.000 DEG C

AC ANALYSIS

V(3)

FREO

3.992E-01

1.000E+04

1.000E-02

6.323E-02

```

**Fig. 12.52** Saída PSpice para o circuito da Fig. 12.53.

Fig. 12.53 Circuito para o Programa 1 PSpice.

Parâmetros JFET (para cada transistor):

$$I_{DQ}$$

= 2,78 mA, $V_{GSQ}$  =  $-$  1,89 V, $g_m$  = 2,64 mS ( $g_m$  = 2,6 mS no Exemplo 12.1)

Resultados ac:

$$A_{v_1} = \frac{V(3)}{V(1)} = \frac{6,323 \times 10^{-2}}{1 \times 10^{-2}} = 6,3 \ (-6,2 \text{ no Exemplo } 12.1)$$

$$A_{v_2} = \frac{V(6)}{V(3)} = \frac{3,992 \times 10^{-1}}{6,323 \times 10^{-2}} = 6,3 \ (-6,2 \text{ no Exemplo 12.1})$$

$$V_o = V(9) = 3,992 \times 10^{-1} = 399 \text{ mV}$$

( $V_o = 384 \text{ mV no Exemplo 12.1})$

O ganho de tensão ac e a tensão ac de saída obtidos no Exemplo 12.1 estão próximos dos valores obtidos no PSpice. Lembre que PSpice usa um modelo mais sofisticado do que o usado no Exemplo 12.1, e que em todos os passos no PSpice consideramse mais casas decimais, o que faz com que os resultados sejam um pouco diferentes.

## PSpice para Windows (Windows Design Center Analysis)

O circuito da Fig. 12.53 pode ser desenhado utilizando-se o programa da MicroSim's Schematics para Windows. A seguir apresenta-se uma breve descrição de como se desenha o circuito mostrado na Fig. 12.54.

1. Selecione o dispositivo J2N3819 da biblioteca eval.slb.

Edit, Model: Edit Instance Model altere Beta = 0,625E-3 e

altere Vto = -4

Copie e cole o segundo JFET no circuito.

- Selecione o componente R da biblioteca analog.slb.

Coloque os valores e os nomes previstos para os vários resistores.

- Selecione o componente C da biblioteca analog.slb.

Coloque os valores e os nomes previstos para os vários capacitores.

- 4. Selecione o componente VSRC da biblioteca source.slb para a fonte dc (usando a Versão 6.0) ou bateria (usando a Versão 6.1 ou posterior).

Coloque o nome  $(V_{ss})$  e o valor (+20 V).

Fig. 12.54 Circuito na versão para Windows para analisar o amplificador JFET de dois estágios.

```

CIRCUIT DESCRIPTION

$N_0002 $N_0001 2.4K

0 $N_0003 680

0 $N_0004 3.3MEG

0 $N_0005 10k

R_RD1

R RS1

R RG1

R RL

$N_0006 $N_0004 0.05uF

0 $N_0003 20uF

$N_0007 $N_0001 2.4K

C CS1

R_RD2

$N_0007 $N_0001 2.4K

0 $N_0008 680

0 $N_0009 3.3MEG

$N_0002 $N_0009 0.05uF

0 $N_0008 20uF

$N_0007 $N_0005 0.05uF

$N_0002 $N_0004 $N_0003 J2N3819-X

$N_0007 $N_0009 $N_0008 J2N3819-X

$N_0001 0 20V

R_RS2

R RG2

C^{T}C2

C_CS2

C_Co

J_J2

J_J3

V_VDD

V_Vi

$N_0006 0 DC 0 AC 10mV SIN 0 10mV 10kHz 0 0 0

. PRINT

AC VM([\$N_0005]) VM([\$N_0006]) VM([\$N_0002]) VM([\$N_0007]) Junction FET MODEL PARAMETERS

J2N3819~X

NJF

VTO

BETA 625.000000E-06

SMALL SIGNAL BIAS SOLUTION

NODE

VOLTAGE

NODE

VOLTAGE

NODE

($N_0001)

($N_0003)

($N_0005)

($N_0007)

($N_0002)

($N_0004)

($N_0006)

20.0000

1.9061

107.9E-06

0.0000

(e000=n2)

107.9E-06

AC ANALYSIS

FREQ

VM($N 0005) VM($N 0006)

3.230E-01 1.000E-02

VM($N_0002)

VM($N_0007)

1.000E+04

6.318E-02

3.231E-01

```

Fig. 12.55 Listagem de saída para o circuito da Fig. 12.54 (editada).

- 5. Selecione o componente VSIN da biblioteca source.slb. Coloque VAMPL = 10 mV e FREQ = 10 kHz.

- Selecione VIEWPOINT da biblioteca special.slb e coloqueo nos terminais de fonte e dreno de ambos os transistores.

- Selecione VPRINT1 da biblioteca special.slb e coloque-o na entrada, nos dois terminais de dreno e na saída.

Dê um duplo clique em cada objeto e faça TRAN = ok, e MAG = ok; desta forma os itens são selecionados para serem mostrados.

Execute o programa para obter o arquivo de saída FIG12-54.OUT. Uma versão editada é apresentada na Fig. 12.55. Compare os valores de polarização de mostrados na listagem com os valores obtidos utilizando-se a versão para DOS do PSpice (Versão 6.0). Compare também as amplitudes dos sinais ac obtidos em ambos os métodos. Os resultados são próximos.

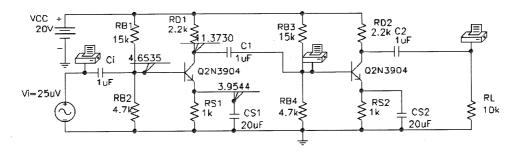

## Programa 12.2. Amplificador TBJ em Cascata

O amplificador TBJ em cascata do Exemplo 12.2 é analisado pela listagem do PSpice da Fig. 12.56 (o circuito é mostrado na Fig. 12.57). O modelo TBJ fornece para transistores idênticos

.MODEL BJT NPN (BF =

$$200 \text{ IS} = 7E - 15$$

)

onde  $\beta=200$  e  $I_S=7\times 10^{-7}$  causa  $V_{BE}=0.7$  V no modelo do PSpice. O sinal ac de entrada é

$$V_i = 25 \mu V$$

, na frequência de 1 kHz [.AC LIN 1 1KH 1KH]

Um resumo dos resultados obtidos é fornecido em seguida.

Polarização dc (cada transistor):

$$V_{B_o} = 4.7 \text{ V}, \qquad V_{E_o} = 4.0 \text{ V}, \qquad V_{C_o} = 11.2 \text{ V}$$

Parâmetros TBJ (cada transistor):

$$I_B = 19.9 \ \mu A$$

$$I_C = 3.98 \ \text{mA}$$

$$(\beta = I_C/I_B = 3.98 \ \text{mA/19.9} \ \mu \text{A} = 200)$$

$$V_{BE} = 0.7 \ \text{V}$$

Resultados ac:

$$A_{v_1} = \frac{V_{o_1}}{V_{i_1}} = \frac{V(3)}{V(1)} = \frac{2,558 \times 10^{-3}}{2,5 \times 10^{-5}}$$

$$= 102,3 \qquad (-102,3 \text{ no Exemplo 12.2})$$

$$A_{v_2} = \frac{V_{o_2}}{V_{i_2}} = \frac{V(6)}{V(3)} = \frac{8,625 \times 10^{-4}}{2,558 \times 10^{-5}}$$

$$= 337.2 \qquad (-338,46 \text{ no Exemplo 12.2})$$

Uma outra comparação dos resultados obtidos pelos dois métodos pode ser feita incluindo  $r_e$ . Da listagem PSpice.

$$RPI = 1.3 \times 10^3 = 1.3 \text{ k}\Omega$$

Esta é a impedância de entrada olhando para a base do TBJ. Uma vez que

$$RPI = r_i = \beta r_a$$

nós podemos escrever

$$r_e = \frac{r_i}{B} = \frac{1.3 \times 10^3}{200} = 6.5 \ \Omega$$

```

Cascaded BJT Amplifier

CIRCUIT DESCRIPTION

VCC 8 0 20V

R1 8 2 15K

R2 2 0 4.7K

R2 2 0 4.7K

RC1 8 3 2.2K

RE1 4 0 1K

R3 8 5 15K

R4 5 0 4.7K

RC2 8 6 2.2K

RE2 7 0 1K

RL 9 0 1MEG

Q1 3 2 4 BJT

Q2 6 5 7 BJT

C1 1 2 10UF

C2 3 5 10UF

C3 6 9 10UF

CS1 4 0 500UF

CS2 7 0 500UF

VI 1 0 AC 25UV

.MODEL BJT NPN(BF=200 IS=7E-15)

AC LIN 1 1KH 1KH

PRINT AC V(1) V(3) V(6) V(9)

OPTIONS NOPAGE

BJT MODEL PARAMETERS

BJT

NPN

7.000000E-15

200

BF

NF

1

NR

SMALL SIGNAL BIAS SOLUTION

VOLTAGE NODE VOLTAGE

0.0000 ( 2) 4.7004

4.7004 ( 6) 11.2430

TEMPERATURE =

27,000 DEG C

NODE VOLTAGE

( 3) 11.2430

( 7) 4.0003

NODE VOLTAGE

( 4) 4.0003

( 8) 20.0000

NODE

0.0000

4.7004

5)

9)

VOLTAGE SOURCE CURRENTS

CURRENT

-1.000E-02

0.000E+00

VCC

VI

TOTAL POWER DISSIPATION

2.00E-01 WATTS

TEMPERATURE = V(9)

AC ANALYSIS

27,000 DEG C

FREQ

V(3)

V(6)

1.000E+03

2.500E-05

2.558E-03

8.625E-01

8.625E-01

```

Fig. 12.56 Saída PSpice para o circuito da Fig. 12.57.

Fig. 12.57 Circuito para o Programa 2 PSpice.

Fig. 12.58 Circuito na versão para Windows para analisar o amplificador TBJ de dois estágios.

## PSpice para Windows (Windows Design Center Analysis)

O circuito da Fig. 12.57 pode ser desenhado utilizando-se o programa da MicroSim para Windows. A seguir apresenta-se uma breve descrição de como se desenha o circuito mostrado na Fig. 12.58.

- Selecione o dispositivo Q2N3904 da biblioteca eval.slb.

Edit, Model: Edit Instance Model

altere Beta = 200

altere Is = 100E-15

Copie e cole o segundo TBJ no circuito.

- Selecione o componente R da biblioteca analog.slb.

Coloque os valores e os nomes previstos para os vários resistores.

- Selecione o componente C da biblioteca analog.slb.

Coloque os valores e os nomes previstos para os vários capacitores.

- 4. Selecione o componente VSRC da biblioteca source.slb para a fonte dc (usando a Versão 6.0) ou bateria (usando a Versão 6.1 ou posterior).

- Coloque o nome (Vcc) e o valor (+20 V).

- 5. Selecione o componente VSIN da biblioteca source.slb. Coloque VAMPL = 25 uV e FREQ = 1 kHz.

- 6. Selecione VIEWPOINT da biblioteca special.slb e coloqueo nos terminais de fonte e dreno de ambos os transistores.

- 7. Selecione VPRINT1 da biblioteca special.slb e coloque-o na entrada, na base do segundo TBJ, e na saída. Dê um duplo clique em cada objeto e faça TRAN = ok e MAG = ok; desta forma os itens são selecionados para serem mostrados.

Execute o programa para obter o arquivo de saída FIG12-59.OUT. Uma versão editada é apresentada na Fig. 12.59. Compare os valores de polarização de mostrados na listagem com os valores obtidos utilizando-se a versão para DOS do PSpice (Versão 6.0). Compare também as amplitudes dos sinais ac obtidos em ambos os métodos. Os resultados são próximos.

```

CIRCUIT DESCRIPTION

Cascaded BJT Amplifier

$N 0002 $N 0001 $N 0003 Q2N3904-X

Q_Q1

R_RD1

$N 0004 $N 0002 2.2k

$N_0003 0 Tk

$N_0004 $N_0001 15k

$N_0001 0 4.7k

$N_0003 0 20uF

R_RS1

R RB1

R RB2

C CS1

C C1

$N 0003

$N_0005

C_Ci

V +20

$N_0006 $N_0001 luF

0 DC 20

SN 0004

Q_Q2

R_RD2

R_RS2

$N_0007

$N_0005 $N_0008 Q2N3904-X

$N_0004 $N_0007 2.2k

$N_0008 0 1k

R RB3

$N_0004

$N_0005 15k

R_RB4

C_CS2

C_C2

SN 0005

0 4.7k

$N_0008

$N 0007 $N 00

$N 0009 0 TOK

$N_0009 luF

R_RL

V Vi

$N_0006 0 DC 0 AC 25uV

+SIN 0 25uV 1kHz 0 0 0

AC VM([$N_0009]) VM([$N_0006]) VM([$N_0005])

.PRINT

NODE

VOLTAGE

NODE

VOLTAGE

11.3790

($N_0002)

($N_0001)

4.6520

($N 0004)

($N_0003)

3.9519

20,0000

0.0000

($N_0005)

($N_0007)

4.6520

3.9519

11.3790

($N 0008

($N 0009

0.0000

TEMPERATURE = 27.000 DEG C

AC ANALYSTS

VM($N 0009) VM($N_0006) VM($N_0005)

FREO

1.460E-03

2.367E-01

2.500E-05

1.000E+03

```

**Fig. 12.59** Listagem do arquivo 12-58.OUT (editada).

```

Darlington Amplifier

CIRCUIT DESCRIPTION

VCC 6 0 18V

RB 6 2 3.3MEG

RE 4 0 390

C2 4 5 0.5UF

RL 5 0 1MEG

Q1 6 2 3 BJT

Q2 6 3 4 BJT

MODEL BJT NPN(BF=89.4)

VI 1 0 AC 100MV

.AC LIN 1 10KH 10KH

.PRINT AC V(1) V(4) V(5)

.OPTIONS NOPAGE

. END

BJT MODEL PARAMETERS

NPN

100.000000E-18

89.4

NF

SMALL SIGNAL BIAS SOLUTION

DLTAGE NODE VOLTAGE

0.0000 ( 2) 9.6513

0.0000 ( 6) 18.0000

TEMPERATURE =

27.000 DEG C

NODE VOLTAGE NO

NODE VOLTAGE

NODE

VOLTAGE

8.0632

5)

VOLTAGE SOURCE CURRENTS

CURRENT

-2.068E-02

TOTAL POWER DISSIPATION

3.72E-01 WATTS

TEMPERATURE = 27.000 DEG C

AC ANALYSIS

1.000E-01

9.936E-02

1.000E+04

9.936E-02

```

Fig. 12.60 Saída PSpice para o circuito da Fig. 12.61.

## Programa 12.3. Circuito Darlington

O circuito Darlington da Fig. 12.12 é analisado pelo programa PSpice da Fig. 12.60 (veja também a Fig. 12.61). Dois dispositivos TBJ idênticos estão conectados formando um dispositivo Darlington. Um valor de BF = 89,4 foi usado tal que

$$\beta^2 = (89.4)^2 = 7992 \approx 8000$$

Polarização dc:

$$V_{B_1} = V(2) = 9,65 \text{ V}$$

$V_{E_2} = V(4) = 8,06 \text{ V}$

fornecendo  $V_{BE}$  (Darlington) = 1,59 V.

Parâmetros do transistor:

$$I_{B_1}=2,53~\mu\text{A},~I_{C_1}=0,23~\text{mA}~(\beta_1=0,23~\text{mA/2},53~\mu\text{A}=90,9)$$

$I_{B_2}=229~\mu\text{A},~I_{C_2}=20,4~\text{mA}~(\beta_2=20,4~\text{mA/229}~\mu\text{A}=89,1)$

Fig. 12.61 Circuito para o Programa 3 PSpice.

Fig. 12.62 Saída PSpice para o circuito da Fig. 12.59.

para um beta Darlington de

$$\beta_D = \beta_1 \beta_2 = (90,9)(89,1) \approx 8100$$

É difícil forçar o modelo do transistor PSpice para casar exatamente com o modelo de transistor ideal usado na Fig. 12.12. Note que os resultados PSpice fornecem

$$V_{BE_1} = 0.736 \text{ V}, \qquad V_{BE_2} = 0.852 \text{ V}$$

enquanto o modelo usado na Fig. 12.12 especifica  $V_{BE}(D) = 1,6$  V (cerca de 0,736 V + 0,852 V).

Operação~ac: Para uma entrada de  $V_i = 100~\mathrm{mV}$ , a saída na listagem PSpice é

$$V_a = V(5) = 9,936E - 2 = 99,36 \text{ mV}$$

fornecendo um ganho amplificador de

$$A_V = \frac{V_o}{V_i} = \frac{V(5)}{V(1)} = \frac{9,936 \times 10^{-2}}{1 \times 10^{-1}} = 0,9936$$

enquanto os resultados no Exemplo 12.10 fornecem  $A_{\nu} = 0,998$ , que está muito próximo.

Fig. 12.63 Circuito para o programa 4 do PSpice.

## Programa 12.4. Circuito Inversor CMOS

Um circuito inversor CMOS é analisado na listagem fornecida na Fig. 12.62 (veja também a Fig. 12.63). Um MOSFET intensificação canal-p, M1, e um MOSFET intensificação canal-n, M2 estão operando como um circuito inversor CMOS. Com a entrada variando de um valor de de 0 V até um valor de de +5 V, a tensão de saída calculada é listada pelo programa PSpice. A variação da tensão de entrada é estabelecida pela linha

a qual varia VI de 0 a 5 V, seu valor final. A listagem apresenta os dados de saída

$$VI = 0 V$$

$V(2) = 5 V$

$VI = 5 V$   $V(2) \approx 0 V$

para mostrar que o circuito opera como um inversor lógico, fornecendo uma tensão de saída oposta.

#### **PROBLEMAS**

#### § 12.2 Conexão em Cascata

- 1. Para o amplificador a JFET em cascata na Fig. 12.64, calcule as condições de polarização de para os dois estágios idênticos, usando JEFTs com  $I_{DSS}=8$  mA e  $V_P=-4,5$  V.

- 2. Para o amplificador a JFET em cascata da Fig. 12.64, usando JFETs idênticos com  $I_{DSS}=8\,\mathrm{mA}$  e  $V_P=-4,5\,\mathrm{V}$ , calcule o ganho de tensão de cada estágio, o ganho global do amplificador, e a tensão de saída,  $V_o$ .

- 3. Se ambos os JFETs no amplificador em cascata da Fig. 12.64 são trocados por outros com especificações de  $I_{DSS}=12$  mA e  $V_P=-3$  V, calcule a polarização de resultante de cada estágio.

- 4. Se ambos os JFETs no amplificador em cascata da Fig. 12.64 são trocados por outros com especificações de  $I_{DSS}=12$  mA,  $V_P=-3$  V e  $y_{os}=25$   $\mu$ S, calcule o ganho de tensão resultante de cada estágio, o ganho global de tensão, e a tensão de saída,  $V_o$ .

- 5. Para o amplificador em cascata da Fig. 12.64 usando JFETs com especificações de  $I_{DSS}=12$  mA,  $V_P=-3$  V e  $y_{os}=25$   $\mu$ S, calcule a impedância de entrada do circuito ( $Z_i$ ) e a impedância de saída ( $Z_o$ ).

- Para o amplificador TBJ em cascata da Fig. 12.65, calcule as tensões de polarização de e as correntes de coletor para cada estágio.

Fig. 12.64 Problemas 1-5, 30-31.

Fig. 12.65 Problemas 6-8, 32.

- Calcule o ganho de tensão de cada estágio e o ganho de tensão ac global para o amplificador TBJ em cascata da Fig. 12.65.

- 8. Para o circuito da Fig. 12.65, calcule a impedância de entrada do circuito  $(Z_i)$  e a impedância de saída  $(Z_o)$ .

- 9. Para o amplificador em cascata da Fig. 12.66, calcule as tensões de polarização de e a corrente de coletor de cada estágio.

- Para o circuito amplificador da Fig. 12.66, calcule o ganho de tensão de cada estágio e o ganho de tensão global do amplificador.

- 11. Calcule a impedância de entrada do circuito  $(Z_i)$  e a impedância de saída  $(Z_o)$  para o amplificador da Fig. 12.66.

#### § 12.3 Conexão Cascode

12. No circuito amplificador cascode da Fig. 12.67, calcule as tensões de polarização de  $V_{B_1}$ ,  $V_{B_2}$  e  $V_{C_2}$ .

- \*13. Para o circuito amplificador cascode da Fig. 12.67, calcule o ganho de tensão,  $A_v$ , e a tensão de saída,  $V_o$ .

- 14. Calcule a tensão ac através de uma carga de 10-k $\Omega$  conectada na saída do circuito na Fig. 12.67.

#### § 12.4 Conexão Darlington

- 15. Para o circuito da Fig. 12.68, calcule a tensão de polarização dc,  $V_{E_2}$ , e a corrente de emissor,  $I_{E_1}$ .

- \*16. Para o circuito da Fig. 12.68, calcule o ganho de tensão do amplificador.

## § 12.5 Par Realimentado

17. Para o circuito com par realimentado da Fig. 12.69, calcule os valores de polarização de de  $V_B$ ,  $V_{C_2}$  e  $I_c$ .

Fig. 12.66 Problemas 9-11.

Fig. 12.67 Problemas 12-14.

Fig. 12.68 Problemas 15-16, 33.

\*18. Calcule a tensão de saída ac para o circuito da Fig. 12.69.

## § 12.6 Circuito CMOS

- 19. Determine quais transistores estão desligados e quais estão ligados no circuito da Fig. 12.70, para uma entrada de:

- (a)  $V_1 = 0 \text{ V}, V_2 = 0 \text{ V}.$ (b)  $V_1 = +5 \text{ V}, V_2 = +5 \text{ V}.$ (c)  $V_1 = 0 \text{ V}, V_2 = +5 \text{ V}.$

- 20. Para o circuito da Fig. 12.70, complete a tabela de tensão abaixo.

| $V_1$ | $V_2$ | $V_o$ |

|-------|-------|-------|

| 0V    | 0V    |       |

| 0V -  | +5V   |       |

| +5V   | 0V    |       |

| +5V   | +5V   |       |

|       |       |       |

Fig. 12.69 Problemas 17-18

Fig. 12.70 Problemas 19-20, 34.

## § 12.7 Circuitos de Fontes de Corrente

21. Calcule a corrente através de uma carga de 2-k $\Omega$  no circuito da Fig. 12.71

Fig. 12.71 Problema 21.

22. Para o circuito da Fig. 12.72, calcule a corrente I.

Fig. 12.72 Problema 22.

\*23. Calcule a corrente *I* no circuito da Fig. 12.73.

## § 12.8 Circuitos Espelhos de Corrente

- 24. Calcule a corrente refletida I no circuito da Fig. 12.74.

- \*25. Calcule as correntes de coletor para  $Q_1$  e  $Q_2$  na Fig. 12.75.

Fig. 12.73 Problema 23.

Fig. 12.74 Problema 24.

Fig. 12.75 Problema 25.

## § 12.9 Circuito Amplificador Diferencial

- 26. Calculé os valores de de  $I_{\rm C}$  e  $V_{\rm C}$  para o transistores casados da Fig. 12.76.

- 27. Calcule os valores de de  $I_C$  e  $V_C$  para os transistores casados da Fig. 12.77.

- \*28. Calcule  $V_o$  no circuito da Fig. 12.78.

- \*29. Calcule  $V_{o}$  no circuito da Fig. 12.79.

## § 12.10 Análise por Computador

\*30. Escreva um programa no PSpice para calcular a tensão de polarização de do amplificador a JFET em cascata da Fig. 12.64, usando  $I_{DSS}=12$  mA e  $V_P=-3$  V.

Fig. 12.76 Problema 26.

Fig. 12.77 Problema 27.

- \*31. Escreva um programa no PSpice para calcular a tensão de saída,  $V_o$  para o circuito a JFET em cascata da Fig. 12.64, usando  $I_{DSS}$  = 12 mA,  $V_P = -3$  V, e  $y_{os} = 25 \mu$ S.

- \*32. Escreva um programa no PSpice para calcular a tensão de saída ac de cada estágio do amplificador a TBJ em cascata da Fig. 12.65.

- \*33. Escreva um programa no PSpice para calcular o ponto de operação do transistor e a tensão de saída ac para o circuito amplificador Darlington da Fig. 12.68.

Fig. 12.78 Problema 28.

Fig. 12.79 Problema 29.

- \*34. Escreva um programa no PSpice para listar as tensões dc dos seguintes conjuntos de entradas para o circuito CMOS da Fig. 12.70.

(a)

$$V_1 = 0 \text{ V}, V_2 = 0 \text{ V}.$$

(b)  $V_1 = 0 \text{ V}, e V_2 = +5 \text{ V}.$

(c)  $V_1 = +5 \text{ V}, V_2 = +5 \text{ V}.$

<sup>\*</sup>Observação: os asteriscos indicam problemas mais difíceis.